# Role of surfaces and dopants in quantum devices and nanowire transistors

**Author:** Carrad, Damon

Publication Date: 2015

DOI: https://doi.org/10.26190/unsworks/2883

### License:

https://creativecommons.org/licenses/by-nc-nd/3.0/au/ Link to license to see what you are allowed to do with this resource.

Downloaded from http://hdl.handle.net/1959.4/55335 in https:// unsworks.unsw.edu.au on 2024-05-02

## Role of surfaces and dopants in quantum devices and nanowire transistors

Author: Damon CARRAD Supervisor: A/Prof Adam MICOLICH

A thesis submitted in fulfilment of the requirements for the degree of Doctor of Philosophy

School of Physics Faculty of Science

December 2015

| PLEASE TYPE                                                                                                        |                                                |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|--|--|--|

| THE UNIVERS                                                                                                        | THE UNIVERSITY OF NEW SOUTH WALES              |  |  |  |  |  |

| Thesis                                                                                                             | s/Dissertation Sheet                           |  |  |  |  |  |

|                                                                                                                    |                                                |  |  |  |  |  |

| Surname or Family name: Carrad                                                                                     |                                                |  |  |  |  |  |

|                                                                                                                    |                                                |  |  |  |  |  |

| First name: Damon                                                                                                  | Other name/s: James                            |  |  |  |  |  |

|                                                                                                                    |                                                |  |  |  |  |  |

| Abbreviation for degree as given in the University calendar: PhD                                                   |                                                |  |  |  |  |  |

|                                                                                                                    |                                                |  |  |  |  |  |

| School: School of Physics                                                                                          | Faculty: Faculty of Science                    |  |  |  |  |  |

|                                                                                                                    |                                                |  |  |  |  |  |

|                                                                                                                    | Title: Role of surfaces and dopants in quantum |  |  |  |  |  |

| devices and nanowire transistors                                                                                   |                                                |  |  |  |  |  |

|                                                                                                                    |                                                |  |  |  |  |  |

|                                                                                                                    |                                                |  |  |  |  |  |

| Abstract 350 words maximum: (PLEASE TYPE)                                                                          |                                                |  |  |  |  |  |

|                                                                                                                    |                                                |  |  |  |  |  |

| Miniaturisation of electronic devices has driven development of high speed, high density processors and memory     |                                                |  |  |  |  |  |

| elements. This process has required extensive ontimisation of semiconductor materials and interfaces as the random |                                                |  |  |  |  |  |

elements. This process has required extensive optimisation of semiconductor materials and interfaces as the random nature of doping increasingly affects device performance and the influence of non-ideal surfaces and interfaces need to be counteracted. As Moore's law for silicon may soon reach its limit, there is a desire to harness electrically efficient III-V semiconductor materials in an economically viable way. There is also a desire to utilise new functionalities brought by quantum mechanics, thermoelectrics and organic materials.

This thesis explores the role of p-type AlGaAs/GaAs heterostructures, self-assembled semiconductor nanowires and organic polymer electrolytes in this broad research programme. My research investigated the impact of background potentials generated by doping and surface states for quantum devices. I developed new wrap-gating techniques for InAs semiconductor nanowires towards economically viable arrays of III-V transistors on silicon substrates. This involved both conventional metal/oxide wrap-gates as well as nanoscale patterning of polymer electrolyte films to both improve the compatibility of organics with nanostructures and seek new functionalities for nanowire transistors. I then used polymer electrolytes to both act as an external dopant, and set the background potential for nanowire thermoelectrics. I also developed proof-of-principle complementary n- and p-type proton-to-electron transducers.

Throughout, I highlight the importance of dopants and surfaces. I show how these non-ideal aspects of semiconductor devices affect performance and attempt to find solutions where possible by, e.g., using sulfur-based surface passivation solutions or polymer electrolytes as an external dopant. Using these examples I illustrate that the drive to develop new technologies leads to new physics on both ends. Imperfections in research devices lead to new understanding of material physics, and once these are overcome, the new functionalities embodied by the devices can be used to study new aspects of nature.

#### Declaration relating to disposition of project thesis/dissertation

I hereby grant to the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or in part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all property rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstracts International (this is applicable to doctoral theses only).

Signature

The University recognises that there may be exceptional circumstances requiring restrictions on copying or conditions on use. Requests for restriction for a period of up to 2 years must be made in writing. Requests for a longer period of restriction may be considered in exceptional circumstances and require the approval of the Dean of Graduate Research.

FOR OFFICE USE ONLY

Date of completion of requirements for Award:

THIS SHEET IS TO BE GLUED TO THE INSIDE FRONT COVER OF THE THESIS

### Abstract

Miniaturisation of electronic devices has driven development of high speed, high density processors and memory elements. This process has required extensive optimisation of semiconductor materials and interfaces as the random nature of doping increasingly affects device performance and the influence of non-ideal surfaces and interfaces need to be counteracted. As Moore's law for silicon may soon reach its limit, there is a desire to harness electrically efficient III-V semiconductor materials in an economically viable way. There is also a desire to utilise new functionalities brought by quantum mechanics, thermoelectrics and organic materials.

This thesis explores the role of p-type AlGaAs/GaAs heterostructures, self-assembled semiconductor nanowires and organic polymer electrolytes in this broad research programme. My research investigated the impact of background potentials generated by doping and surface states for quantum devices. I developed new wrapgating techniques for InAs semiconductor nanowires towards economically viable arrays of III-V transistors on silicon substrates. This involved both conventional metal/oxide wrap-gates as well as nanoscale patterning of polymer electrolyte films to both improve the compatibility of organics with nanostructures and seek new functionalities for nanowire transistors. I then used polymer electrolytes to both act as an external dopant, and set the background potential for nanowire thermoelectrics. I also developed proof-of-principle complementary n- and p-type proton-to-electron transducers.

Throughout, I highlight the importance of dopants and surfaces. I show how these non-ideal aspects of semiconductor devices affect performance and attempt to find solutions where possible by, e.g. using sulfur-based surface passivation solutions or polymer electrolytes as an external dopant. Using these examples I illustrate that the drive to develop new technologies leads to new physics on both ends. Imperfections in research devices lead to new understanding of material physics, and once these are overcome, the new functionalities embodied by the devices can be used to study new aspects of nature.

#### **ORIGINALITY STATEMENT**

'I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.'

17/12/2015 Signed ..... •

Date

#### COPYRIGHT STATEMENT

'I hereby grant the University of New South Wales or its agents the right to archive and to make available my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known, subject to the provisions of the Copyright Act 1968. I retain all proprietary rights, such as patent rights. I also retain the right to use in future works (such as articles or books) all or part of this thesis or dissertation.

I also authorise University Microfilms to use the 350 word abstract of my thesis in Dissertation Abstract International (this is applicable to doctoral theses only).

I have either used no substantial portions of copyright material in my thesis or I have obtained permission to use copyright material; where permission has not been granted I have applied/will apply for a partial restriction of the digital copy of my thesis or dissertation."

Signed

2015

Date

#### AUTHENTICITY STATEMENT

'I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis. No emendation of content has occurred and if there are any minor variations in formatting, they are the result of the conversion to digital format.'

| Signed | Alt        |

|--------|------------|

| Date   | 17/12/2015 |

# Acknowledgements

The results in this thesis would not have been possible without the work of so many people. It's been a privilege to work with passionate scientists with a strong desire to collaborate, help and contribute.

First and foremost a huge debt of gratitude is owed to Adam Micolich. He has been an amazing supervisor, and has consistently gone above and beyond in ensuring that we have been able to produce the best science we possibly could. None of this thesis would have been possible without his vision and support. I am also hugely grateful for the opportunities to travel around Australia and the world to collect data and present at conferences. It has also been a pleasure to have someone as a supervisor who is just a straight up good guy, with a faultlessly excellent taste in beer.

Secondly, I must thank Adam Burke, who was my partner in crime for the vast majority of research that went into this thesis. He taught me everything about device fabrication and electrical measurements, and his patience and skill in explaining everything made the whole process smooth and easy. I couldn't have asked for a better person to work with, and I really hope we do more together throughout our careers.

I would also like to thank the other members Nanoelectronics Group members, Jan Gluschke, Rifat Ullah and Roman Lyttleton. Each contributed a lot to this thesis, either directly with fabrication and experiments or indirectly with helping to run a good lab. Massive thanks also to Jan for proof-reading this thesis. I'd also like to thank Jack Cochrane for the excellent job he does in maintaining everything in the labs, and sincerely hope he's able to keep doing so for a while yet.

Thanks are also due to my collaborators and co-authors. First of all, to Peter Reece for being my co-supervisor, doing/helping with the PL measurements and having some good discussions about them with me, and for always sharing a joke. Thanks also to Oleh Klochan, Andrew See and Alex Hamilton from the QED group for helping out with the dilution fridge and the many other helpful discussions over the years, along with Karina, Sarah, Daisy, LaReine, Ashwin, Roy and Jason. I must extend a massive amount of appreciation to Bernard Mostert and Paul Meredith at the University of Queensland for hosting me twice, and to Bernard in particular for working with me non-stop to collect (and understand!) so much good data. I am really grateful for the experience. I also thank Heiner Linke and Sofia Fahlvik Svensson for bringing us a really interesting experiment to work on, and to Martin Leijnse for providing the great insight into the meaning of the results. Thanks also to Heiner for hosting me in Lund, Sweden, along with Sofia, Kristian and Gustav, and to Mercy, Cassie, Jan and all the other Lund folk for making it an enjoyable stay. I also must acknowledge Kristian, Gustav and Sofia as well as Hannah Joyce, Hark Hoe Tan and Chennupati Jagadish from ANU for supplying us with the nanowires our devices were based on. Thanks also are extended to Andreas Wieck and his group for growing and supplying the AlGaAs/GaAs wafers. I thank Helen Rutlidge and Bill Bin Gong for performing the ICPMS and XPS contained in this thesis, and Tim Bray and Craig Johnson for assistance with the PL. Finally, I'd like to extend appreciation to the ANFF staff, past and present, for all the assistance in the cleanrooms.

I would also like to thank the Australian Nanotechnology Network for funding some of my travels and everything that they do to contribute to the community in Australia, including putting on excellent conferences and providing opportunities to young researchers. I also thank the Graduate Research School at UNSW for the funding that enabled me to visit Lund and Austin.

More personally, I would like to thank Pat McMillan. The experience in third year lab was a very important step into the research world and contributed a huge amount to my philosophy on how to do science, how to understand science, and also how to teach it. I will also be eternally grateful to Anthony Mills, without whom I never would have done physics in the first place.

I'd like to also thank Tim, Tim, Alex, Alex, Chidge, Ana, Kellie, Ahmad and everyone else in my undergrad cohort for helping me stick with it by somehow making uni fun. Thanks in particular to Ana for tipping me off about this LaTeX template and being a cool housemate. And thanks also to all my friends and everyone in the musical sphere (esp. Shelby, a strong component of both) for keeping me sane and making Sydney a worthwhile place to throw away money on rent.

I have an endless amount of gratitude and thanks for my parents and sister for their constant support in every way and providing an example that I know I'm lucky to have, and to dad for proofing this thesis too. And finally, I need to express something that goes beyond 'thanks' and gratitude to Leila for simply being my love and all that brings to me, and for the life we are building together.

### Publications arising from this work

#### **Refereed Journal Publications**

D. J. Carrad, A. M. Burke, P. J. Reece, R. W. Lyttleton, D. E. J. Waddington, A. Rai, D. Reuter, A. D.Wieck & A. P. Micolich. 'The effect of (NH<sub>4</sub>)<sub>2</sub>S<sub>x</sub> passivation on the (311)A GaAs surface and its use in AlGaAs/GaAs heterostructure devices.' *Journal of Physics: Condensed Matter* 25, p. 325304 (2013)

My contribution: I worked closely with Dr Adam Burke on the fabrication and measurement of the electrical devices. I prepared samples for the photoluminescence and X-ray photoelectron spectroscopy and performed some of the photoluminescence measurements. I analysed the data and wrote the paper with A/Prof Adam Micolich. This paper is discussed in Chapter 3.

D. J. Carrad, A. M. Burke, O. Klochan, A. M. See, A. R. Hamilton, A. Rai, D. Reuter, A. D. Wieck & A. P. Micolich. 'Determining the stability and activation energy of Si acceptors in AlGaAs using quantum interference in an open hole quantum dot.' *Physical Review B* 89, p. 155313 (2014)

My contribution: I fabricated and measured the electrical properties of the etched open hole quantum dot with Dr Adam Burke. I analysed the data and wrote the paper with A/Prof Adam Micolich. This paper is discussed in Chapter 3.

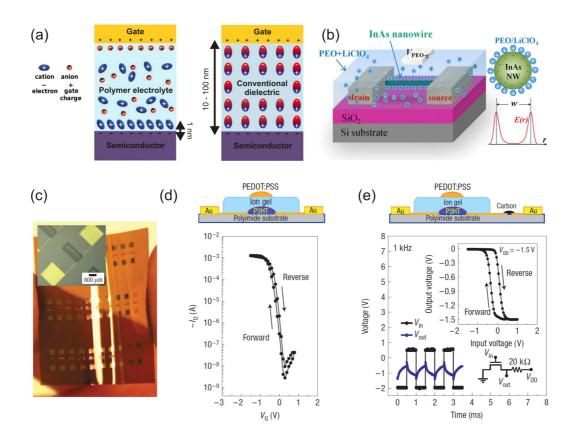

D. J. Carrad, A. M. Burke, R. W. Lyttleton, H. J. Joyce, H. H. Tan, C. Jagadish, K. Storm, H. Linke, L. Samuelson & A. P. Micolich. 'Electron-Beam Patterning of Polymer Electrolyte Films To Make Multiple Nanoscale Gates for Nanowire Transistors.' *Nano Letters* 14, pp. 94–100 (2014)

My contribution: I developed the electron-beam patterning process, fabricated devices and conducted electrical measurements with the help of Dr Adam Burke and Roman Lyttleton. I analysed the data and wrote the paper with A/Prof Micolich. This paper is discussed in Chapter 4.

A. M. Burke, D. J. Carrad, J. G. Gluschke, K. Storm, S. Fahlvik Svensson, H. Linke, L. Samuelson & A. P. Micolich. 'InAs Nanowire Transistors with Multiple, Independent Wrap-Gate Segments.' *Nano Letters* 15, pp. 2836–2843 (2015)

My contribution: I assisted Dr Adam Burke and A/Prof Adam Micolich in developing the process for fabricating multiple-wrap gated devices. I also assisted with electrical measurements and development of the logic programs used to evaluate wrap-gate electrical balance. This paper is discussed in Chapter 4.

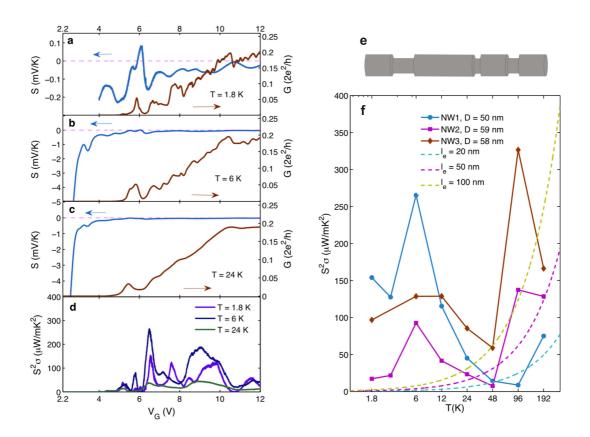

S. Fahlvik Svensson, A. M. Burke, D. J. Carrad, M. Leijnse, H. Linke & A. P. Micolich. 'Using Polymer Electrolyte Gates to set-and-freeze Threshold Voltage and Local Potential in Nanowire-based Devices and Thermoelectrics.' Advanced Functional Materials 25, pp. 255–262 (2015)

My contribution: This work was highly collaborative. I worked with Sofia Fahlvik Svensson to fabricate the device. Sofia, Dr Adam Burke and myself worked together to obtain the electrical measurements. All authors contributed to the interpretation of the data. Sofia, A/Prof Adam Micolich and myself wrote the paper. This paper is discussed in Chapter 5.

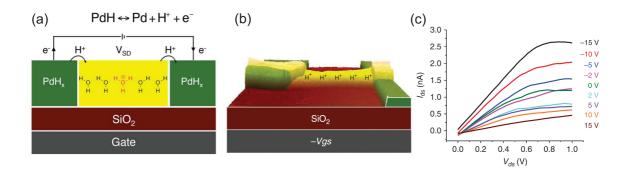

D. J. Carrad, A. B. Mostert, A. R. Ullah, A. M. Burke, H. J. Joyce, H. H. Tan, C. Jagadish, P. Meredith & A. P. Micolich. 'n- and p-type proton-to-electron transducers based on III-V nanowires' *Manuscript in preparation*

My contribution: I fabricated devices with help from Rifat Ullah and Dr Adam Burke. I worked closely with Dr Bernard Mostert to obtain the electrical measurements. I am in the process of writing this paper with Bernard and A/Prof Adam Micolich. This paper is discussed in Chapter 6.

#### **Refereed Conference Proceedings**

D. Carrad, A. Burke, S. Fahlvik Svensson, R. Lyttleton, H. Joyce, H. H. Tan, C. Jagadish, K. Storm, L. Samuelson, H. Linke & A. Micolich. 'Nanoscale polymer electrolytes: Fabrication and applications using nanowire transistors.' In: 2014 Conference on Optoelectronic and Microelectronic Materials Devices (COMMAD), pp. 286–289 (2014)

This presentation was based on the results collected for publications 3 and 6 above.

# Contents

| A              | bstra  | .ct            |                                                            |   |   | iii          |

|----------------|--------|----------------|------------------------------------------------------------|---|---|--------------|

| 0              | rigina | ality S        | tatement                                                   |   |   | $\mathbf{v}$ |

| $\mathbf{A}$   | cknov  | wledge         | ements                                                     |   |   | vii          |

| $\mathbf{P}_1$ | ublica | ations         |                                                            |   |   | x            |

| $\mathbf{C}$   | onter  | $\mathbf{nts}$ |                                                            |   | 2 | xiii         |

| A              | bbrev  | viation        | IS                                                         |   | x | vii          |

| $\mathbf{P}$   | hysic  | al Con         | astants                                                    |   | 2 | xix          |

| Sy             | ymbo   | ls             |                                                            |   |   | xx           |

| 1              | Intr   | oducti         | ion and background                                         |   |   | 1            |

|                | 1.1    | Introd         | luction and chapter outline                                |   |   | 1            |

|                | 1.2    | The fi         | eld-effect transistor                                      | • |   | 5            |

|                |        | 1.2.1          | Basic applications: switching and amplification $\ldots$ . | • | • | 8            |

|                | 1.3    | Non-io         | deal properties of real devices                            | • | • | 10           |

|                |        | 1.3.1          | Doping and bulk impurities                                 |   |   | 10           |

|                |        | 1.3.2          | Surface states and interface states                        | • |   | 12           |

|                |        |                | 1.3.2.1 Surface state passivation                          |   |   | 15           |

|                | 1.4    |                | tum physics of low-dimensional systems                     |   |   | 17           |

|                |        | 1.4.1          | 2D systems; two dimensional electron/hole gas              |   |   | 18           |

|                |        |                | 1.4.1.1 High electron/hole mobility transistors            |   |   | 20           |

|                |        | 1.4.2          | 1D systems; quantum wires and quantum point contacts       |   |   | 22           |

|                |        | 1.4.3          | 0D systems; quantum dots and billiards                     |   |   | 24           |

|                |        | 1.4.4          | Remote ionised impurities and quantum transport            |   |   | 30           |

|                |        | 1.4.5          | Instability in $p$ -type GaAs/AlGaAs heterostructures      | • | • | 34           |

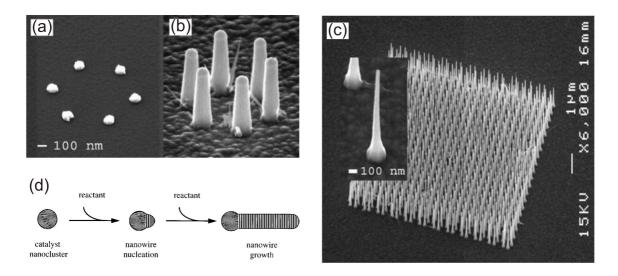

|                | 1.5    |                | ssembled semiconductor nanowires                           | • | • | 38           |

|                |        | 1.5.1          | Motivation                                                 |   |   | 38           |

|          |     | 1.5.2         | Growth principles and advantages                                  |           |

|----------|-----|---------------|-------------------------------------------------------------------|-----------|

|          |     | 1.5.3         | Nanowire FETs                                                     |           |

|          |     | 1.5.4         | Quantum systems in nanowires                                      |           |

|          |     | 1.5.5         | Thermoelectrics and nanowires                                     |           |

|          | 1.6 | Organ         | ic electronics and ionic transport                                |           |

|          |     | 1.6.1         | Polymer electrolytes                                              |           |

|          |     | 1.6.2         | Proton transport and biological applications                      | . 53      |

|          | 1.7 | Summ          | ary                                                               | . 56      |

| <b>2</b> | Me  | thods         |                                                                   | <b>59</b> |

|          | 2.1 | Fabric        | ation and micro-/nano-lithography background                      | . 59      |

|          |     | 2.1.1         | Photolithography                                                  |           |

|          |     | 2.1.2         | Electron beam lithography                                         |           |

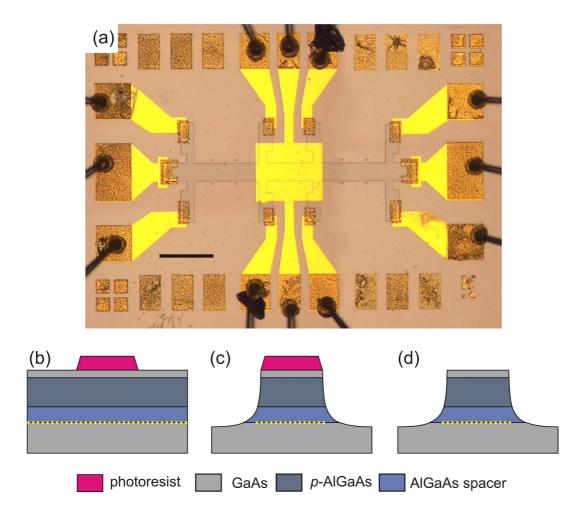

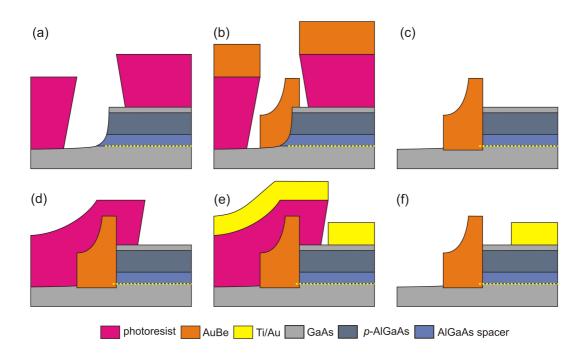

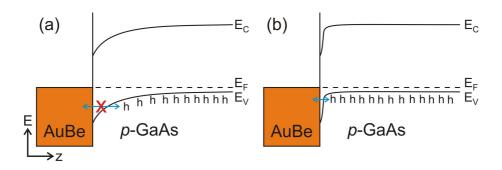

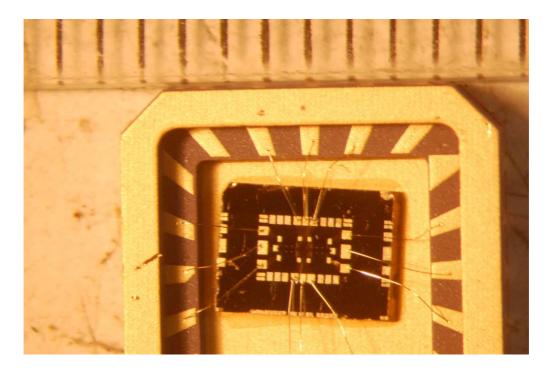

|          | 2.2 | <i>p</i> -AlG | aAs/GaAs device fabrication                                       |           |

|          |     | 2.2.1         | Sulfur passivation                                                |           |

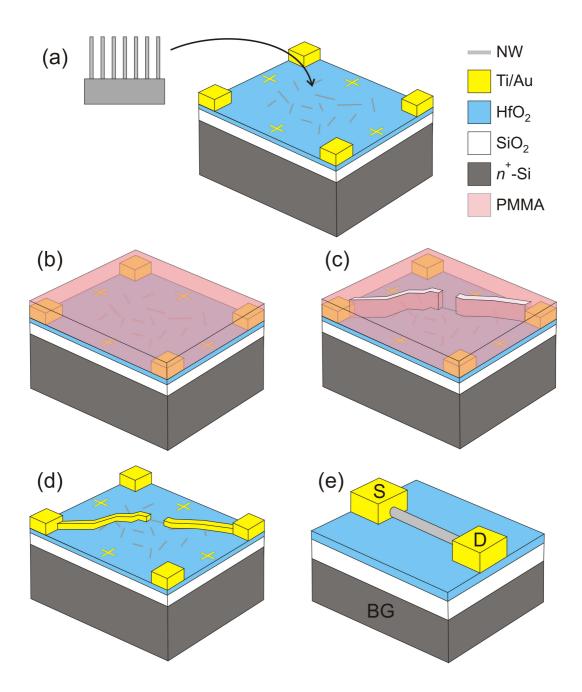

|          | 2.3 |               | ET fabrication                                                    |           |

|          |     | 2.3.1         | Substrate-gated NWFETs                                            |           |

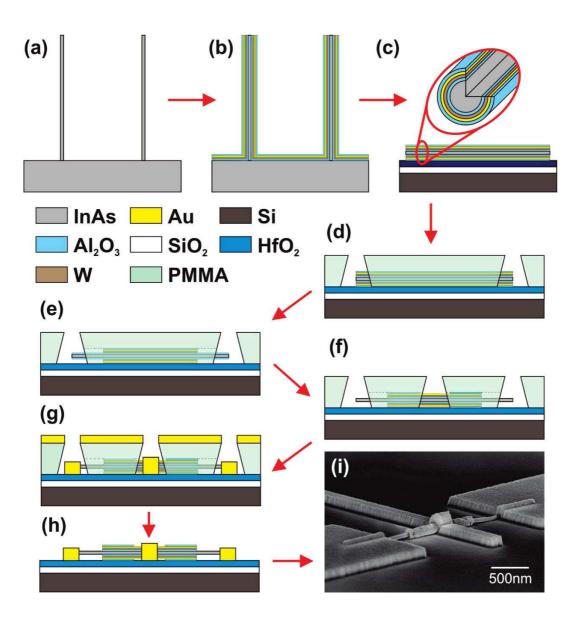

|          |     | 2.3.2         | Wrap-gated NWFETs                                                 |           |

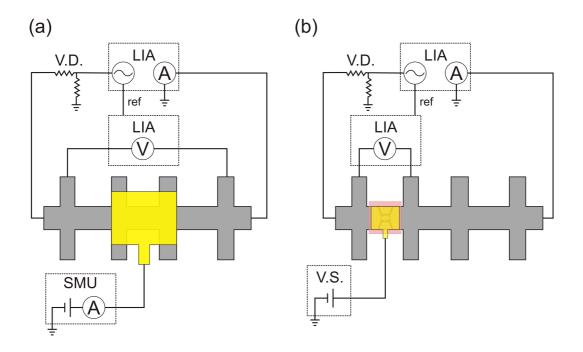

|          | 2.4 | Experi        | imental methods and measurement systems                           |           |

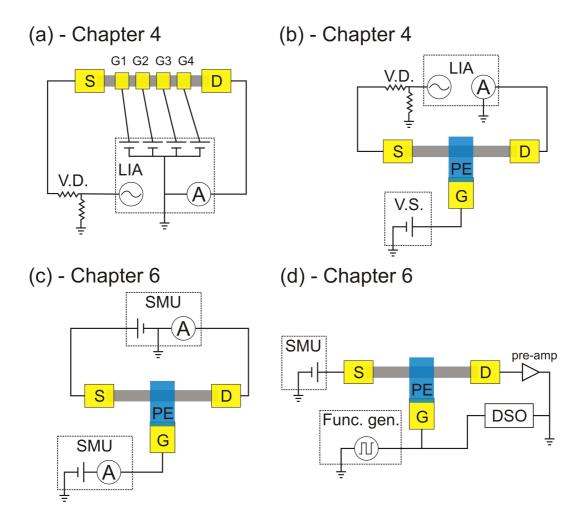

|          |     | 2.4.1         | Electrical characterisation                                       |           |

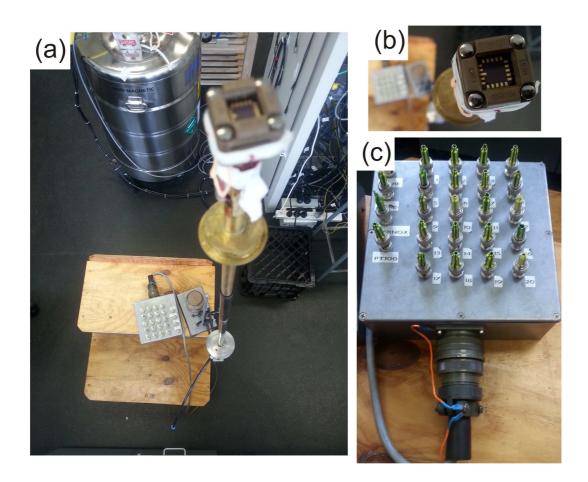

|          |     | 2.4.2         | Cryogen dewar and dipstick                                        | . 85      |

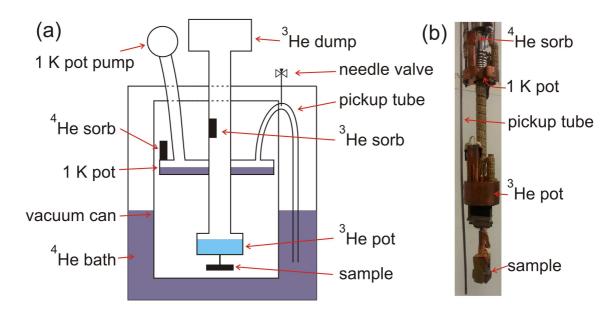

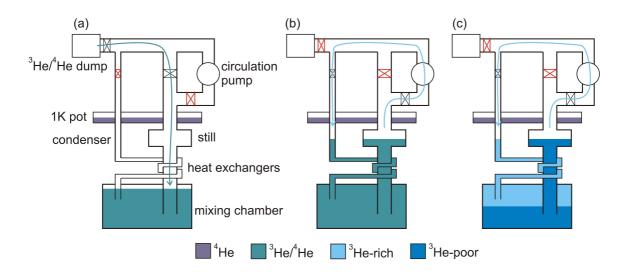

|          |     | 2.4.3         | Heliox <sup>3</sup> He cryostat                                   |           |

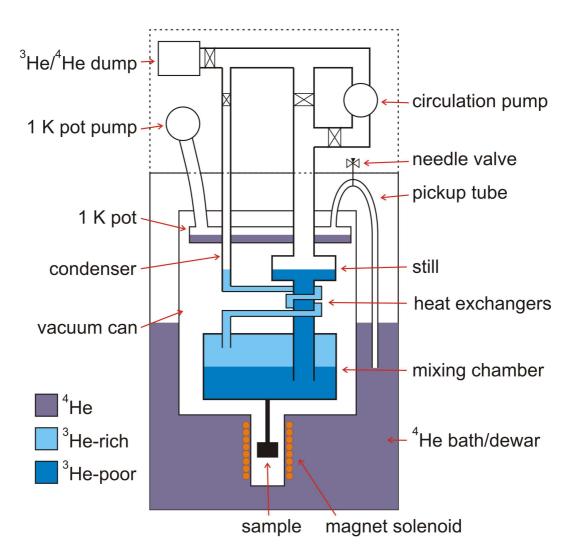

|          |     | 2.4.4         | Kelvinox K100 dilution refrigerator                               |           |

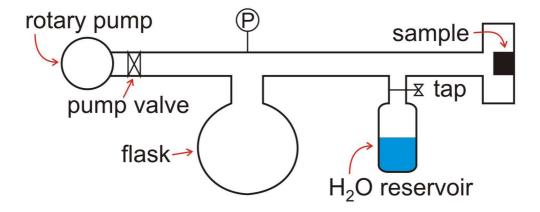

|          |     | 2.4.5         | Hydration dependent measurement chamber                           |           |

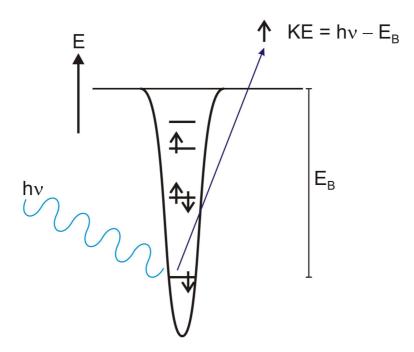

|          |     | 2.4.6         | Photoluminescence and X-ray photoelectron spectroscopy .          |           |

|          | 2.5 | Summ          | ary                                                               | . 98      |

| 3        | Res | ults• ′       | The impact of surfaces and dopants on instability i               | n         |

| J        |     |               | GaAs/GaAs heterostructures                                        | 101       |

|          |     |               | cy of $(NH_4)_2S_x$ solutions on the (311)A GaAs surface          | . 102     |

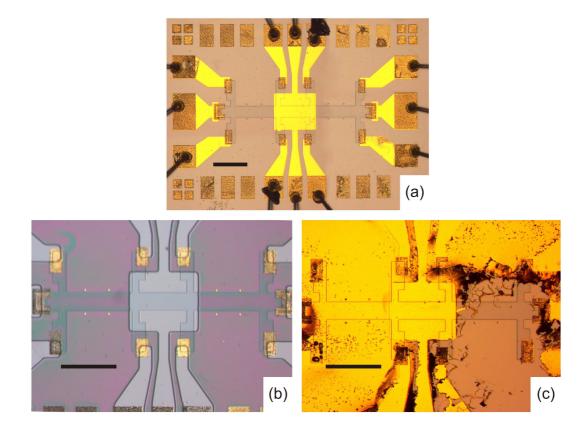

|          | 0.1 | 3.1.1         | Experiment and sample outline $\ldots$                            |           |

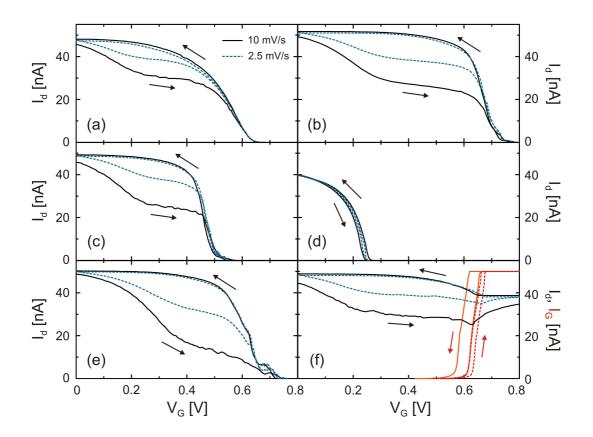

|          |     | 3.1.2         | Performance of $(NH_4)_2S_x$ treated heterostructure devices .    |           |

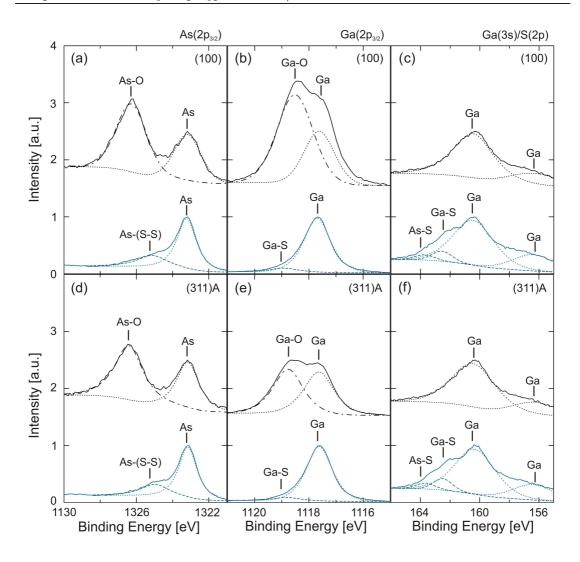

|          |     | 3.1.3         | XPS of $(NH_4)_2S_x$ treated surfaces                             |           |

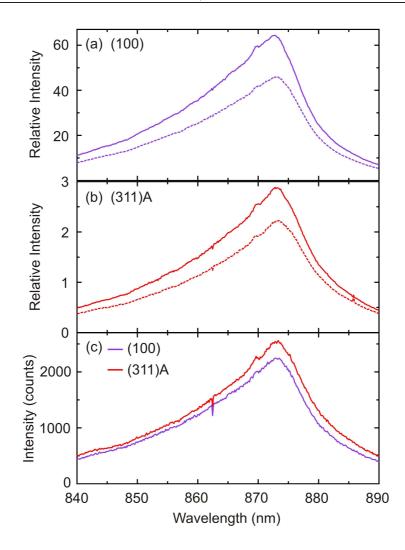

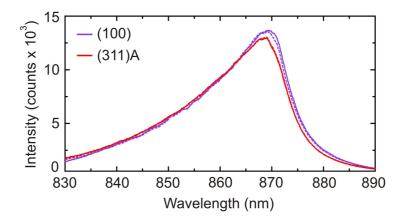

|          |     | 3.1.4         | Photoluminescence of $(NH_4)_2S_x$ treated wafers                 |           |

|          |     | 3.1.5         | Possible causes of ineffective passivation $\ldots \ldots \ldots$ |           |

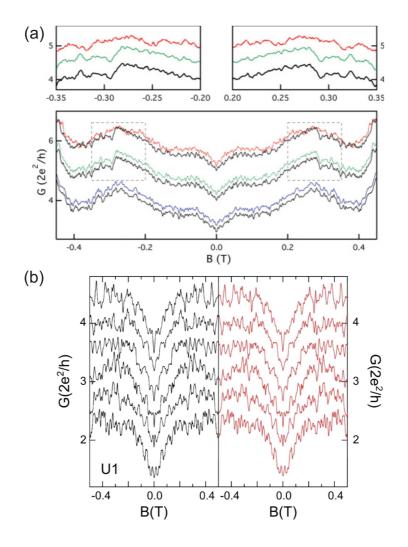

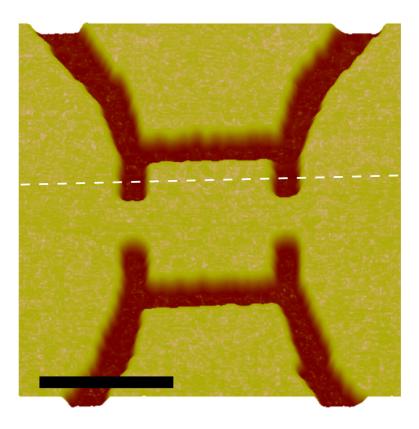

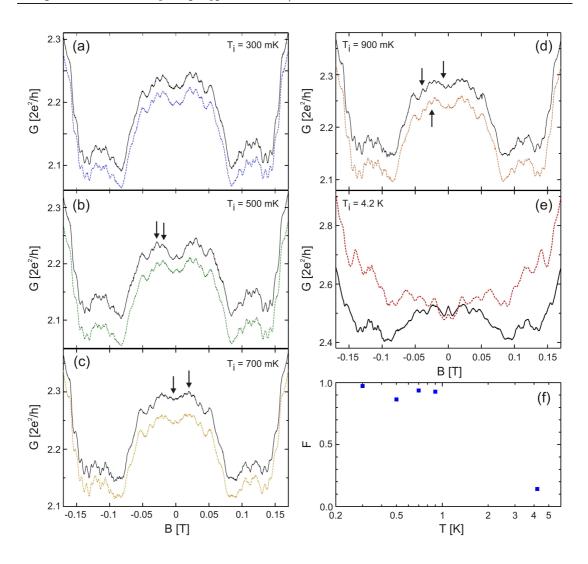

|          | 3.2 |               | magnetoconductance fluctuations to detect changes in dopant       | . 110     |

|          | 0.2 | 0             |                                                                   | . 115     |

|          |     | 3.2.1         | Background, sample and methods                                    |           |

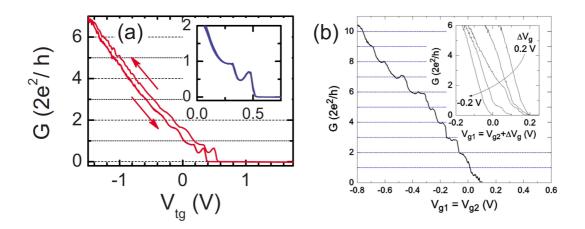

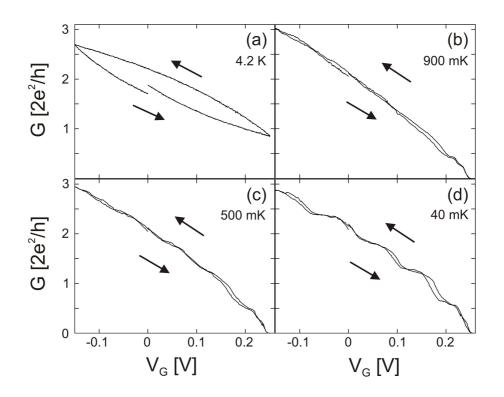

|          |     | 3.2.2         | Gate characterisation                                             |           |

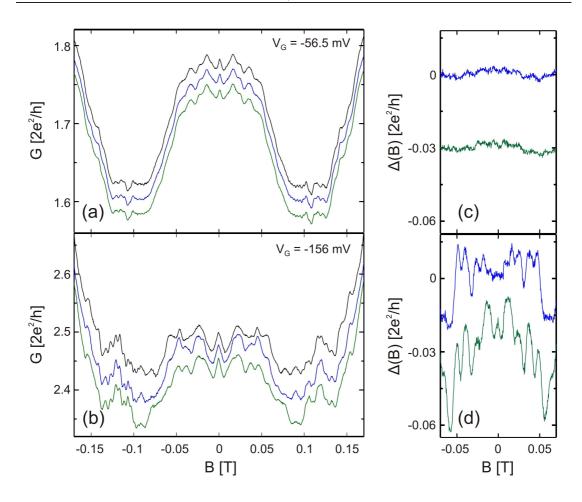

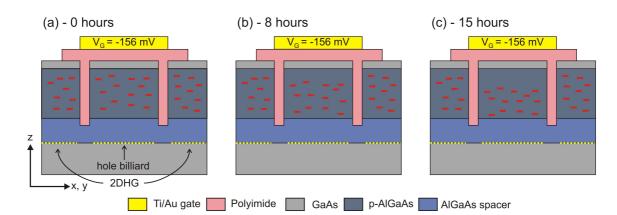

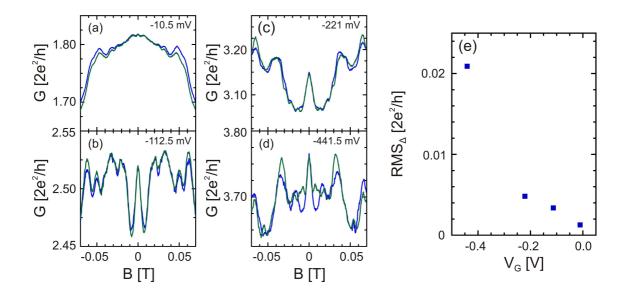

|          |     | 3.2.3         | Temporal stability of MCF at constant $V_G$                       |           |

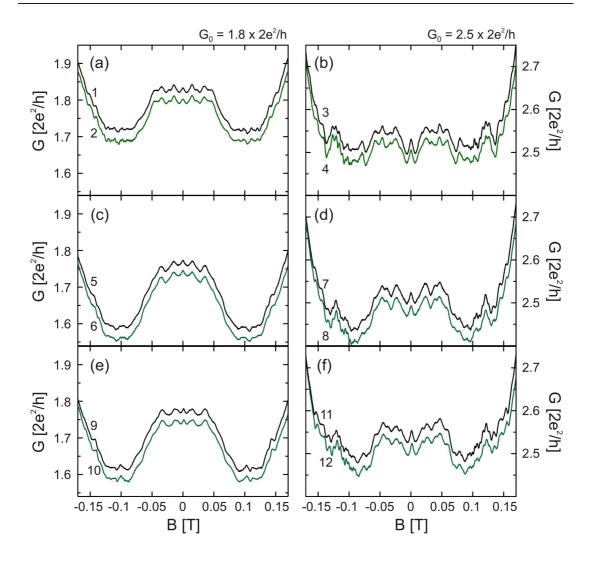

|          |     | 3.2.4         | Evolution of MCF with gate modulation                             |           |

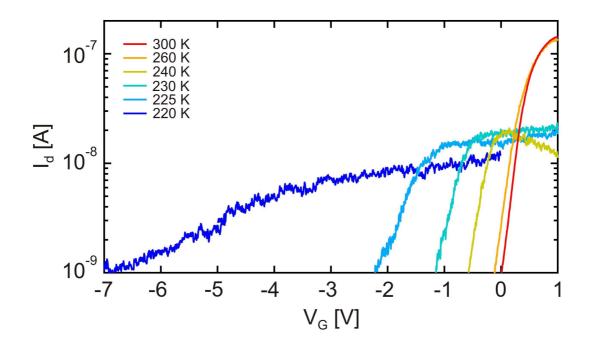

|          |     | 3.2.5         | Thermal cycling and Si-acceptor activation energy                 |           |

|          | 3.3 |               | sion                                                              |           |

| 4        | Dar | ]+~. A        | dropped motion methods for some mine transitions                  | 100       |

| 4        | nes | ouns: A       | Advanced gating methods for nanowire transistors                  | 133       |

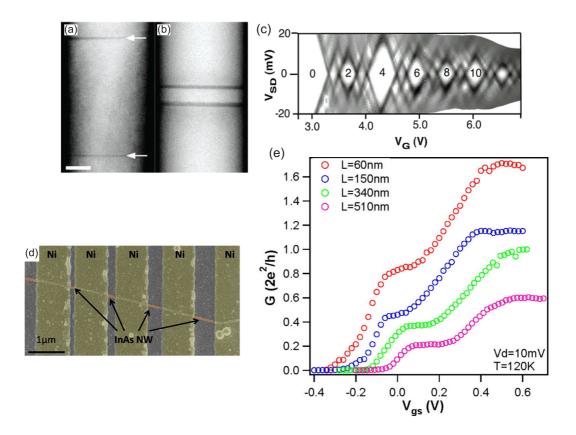

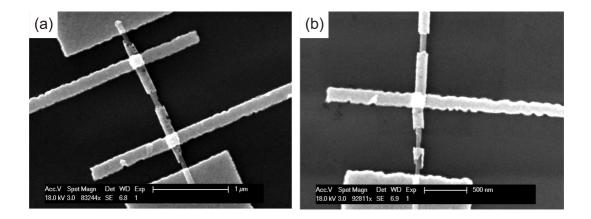

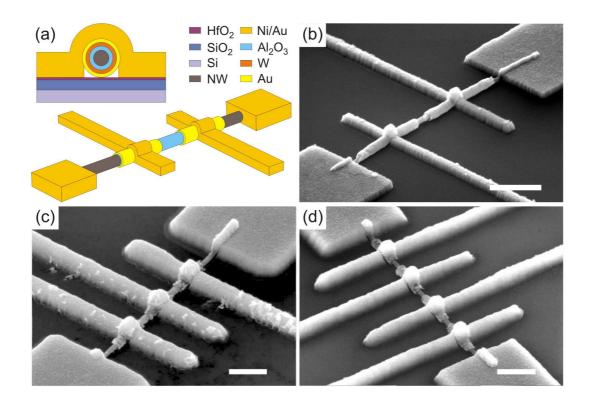

| anowires using multiple metal/oxide wrap-gates                                 | . 133              |

|--------------------------------------------------------------------------------|--------------------|

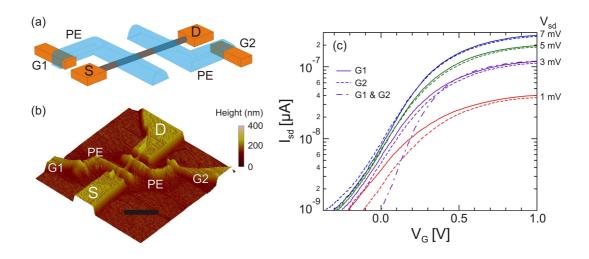

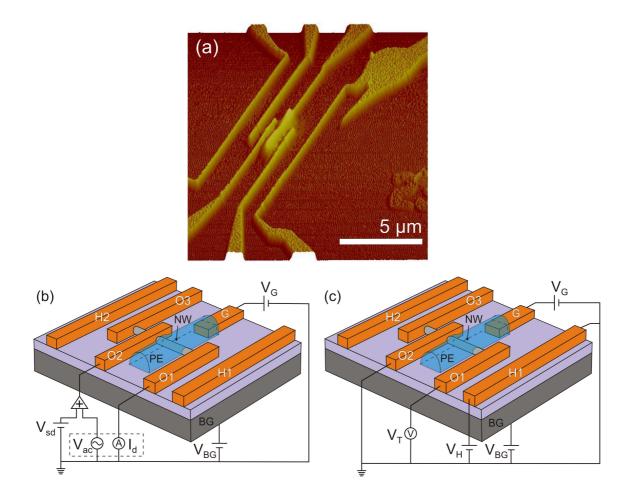

| brication process                                                              | . 135              |

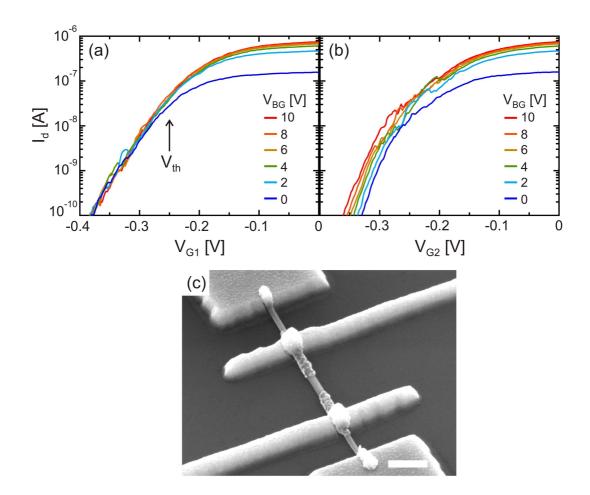

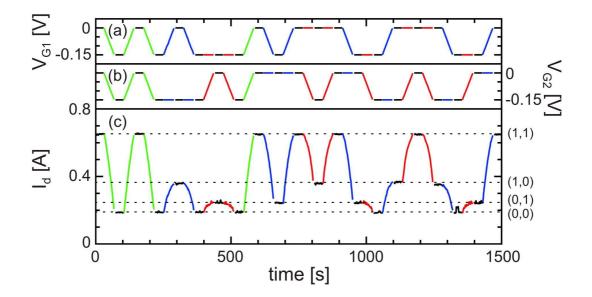

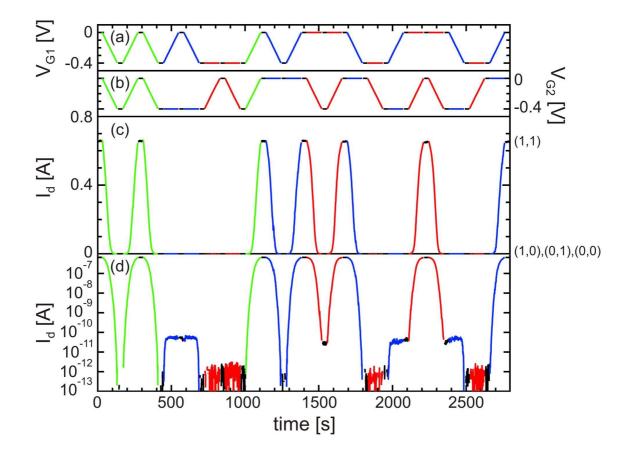

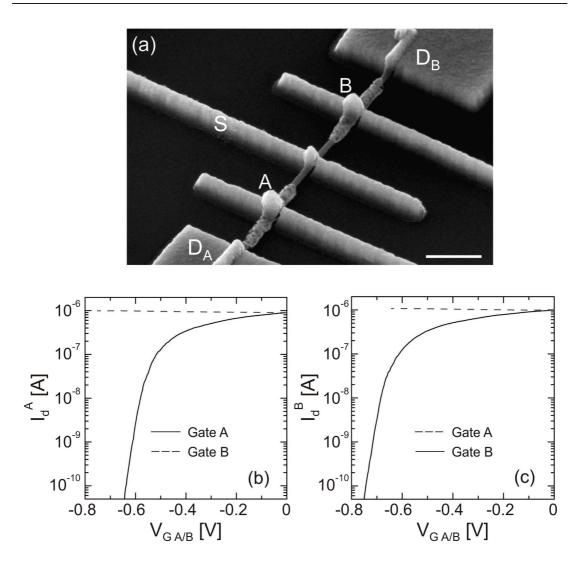

| ectrical characterisation of the two-gate device                               | . 139              |

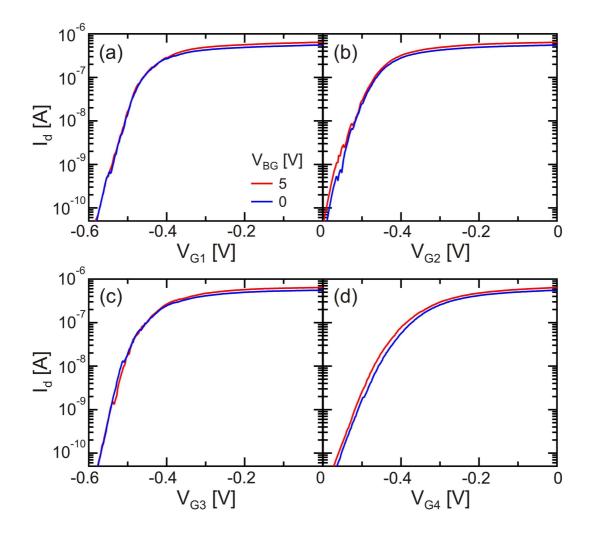

| ectrical characterisation of the four-gate device                              | . 145              |

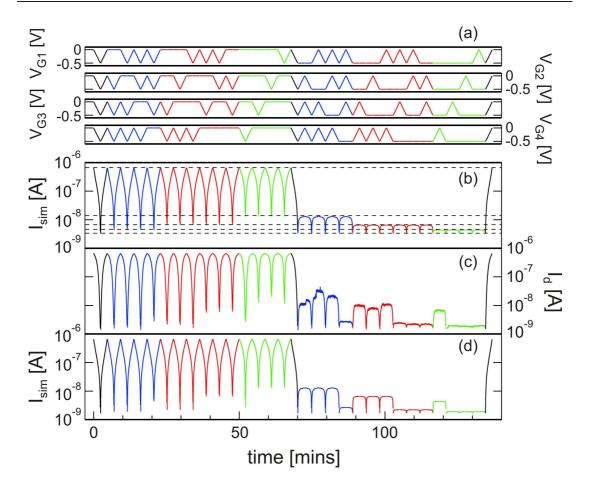

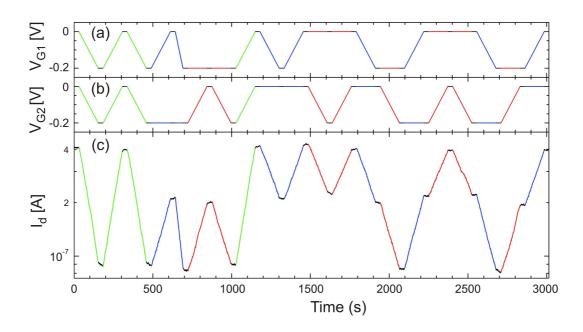

| ultiple transistors on the same nanowire $\ldots \ldots \ldots$                | . 149              |

| ımmary                                                                         | . 151              |

| anowires using nanoscale patterned polymer electrolytes .                      | . 152              |

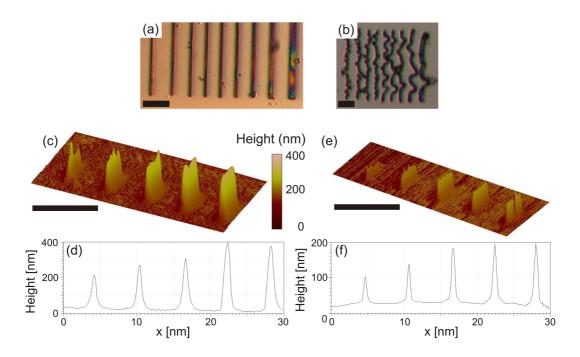

| ectron beam patterning of $PEO/LiClO_4$                                        | . 153              |

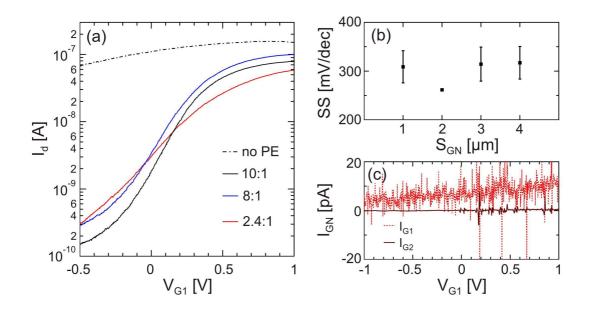

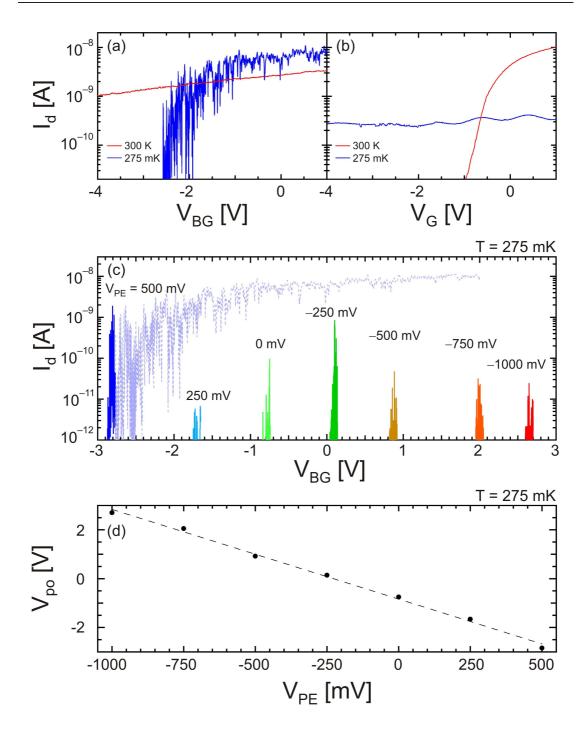

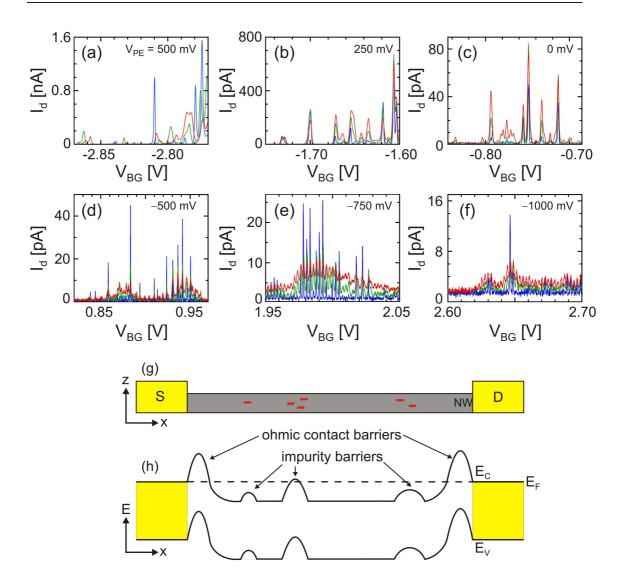

| ngle PE-gated nanowire transistors                                             | . 156              |

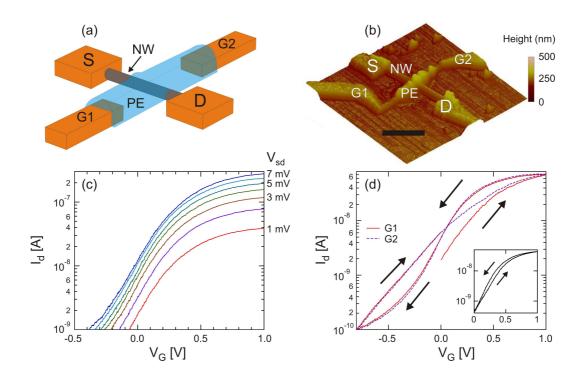

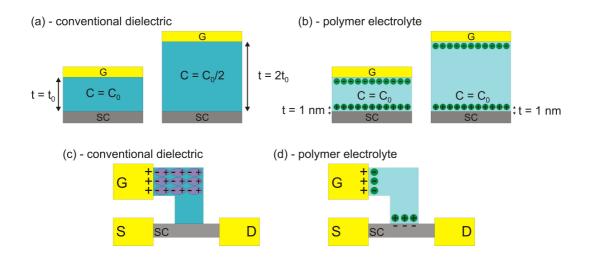

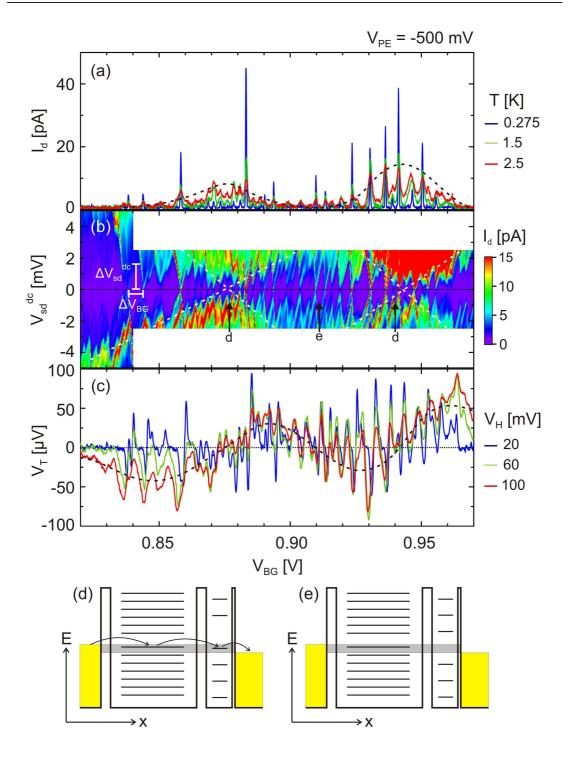

| al PE-gated nanowire transistors                                               | . 163              |

| n                                                                              | . 166              |

|                                                                                |                    |

|                                                                                |                    |

|                                                                                | 169                |

|                                                                                |                    |

|                                                                                |                    |

|                                                                                |                    |

|                                                                                |                    |

|                                                                                |                    |

| a                                                                              | . 187              |

| tons in poly(ethylene oxide)                                                   | 189                |

| n; a control experiment                                                        | . 189              |

| ace on $H_2O$ concentration $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | . 192              |

| behaviour and ionic conductivity                                               | . 198              |

| entary $p$ -GaAs devices $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          | . 207              |

| cansducer applications                                                         | . 210              |

| nd conclusions                                                                 | 217                |

|                                                                                | Abrication process |

### Bibliography

$\mathbf{221}$

# Abbreviations

| 2DEG          | 2-dimensional electron gas                                                                                                                                                                                                                                                                      |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2DHG          | 2-dimensional hole gas                                                                                                                                                                                                                                                                          |  |

| AFM           | Atomic force microscope/microscopy                                                                                                                                                                                                                                                              |  |

| ALD           | Atomic layer deposition                                                                                                                                                                                                                                                                         |  |

| CB            | Conduction band                                                                                                                                                                                                                                                                                 |  |

| CMOS          | $\mathbf{C} \mathbf{o} \mathbf{m} \mathbf{e} \mathbf{t} \mathbf{a} \mathbf{l} \mathbf{-} \mathbf{o} \mathbf{x} \mathbf{i} \mathbf{d} \mathbf{e} \mathbf{-} \mathbf{s} \mathbf{e} \mathbf{m} \mathbf{i} \mathbf{c} \mathbf{o} \mathbf{d} \mathbf{u} \mathbf{c} \mathbf{t} \mathbf{o} \mathbf{r}$ |  |

| DSO           | $\mathbf{D}$ igital <b>s</b> ignal <b>o</b> scilloscope                                                                                                                                                                                                                                         |  |

| EBL           | Electron beam lithography                                                                                                                                                                                                                                                                       |  |

| EDL           | Electric double layer                                                                                                                                                                                                                                                                           |  |

| FET           | Field-effect transistor                                                                                                                                                                                                                                                                         |  |

| HEMT          | $\mathbf{H}$ igh electron mobility transistor                                                                                                                                                                                                                                                   |  |

| HHMT          | $\mathbf{H}$ igh $\mathbf{h}$ ole $\mathbf{m}$ obility $\mathbf{t}$ ransistor                                                                                                                                                                                                                   |  |

| LIA           | Lock-in amplifier                                                                                                                                                                                                                                                                               |  |

| MCF           | $\mathbf{M} agneto \mathbf{c} onductance \ \mathbf{f} luctuations$                                                                                                                                                                                                                              |  |

| MOSFET        | $\mathbf{M} etal\textbf{-o} xide\textbf{-s} emiconductor \ \mathbf{f} ield\textbf{-e} ffect \ \mathbf{t} ransistor$                                                                                                                                                                             |  |

| NMP           | N-methyl-2- $p$ yrrolidone                                                                                                                                                                                                                                                                      |  |

| $\mathbf{NW}$ | Nanowire                                                                                                                                                                                                                                                                                        |  |

| NWFET         | Nanowire field-effect transistor                                                                                                                                                                                                                                                                |  |

| $\mathbf{PE}$ | Polymer electrolyte                                                                                                                                                                                                                                                                             |  |

| PEO           | $\mathbf{P}$ oly( <b>e</b> thylene <b>o</b> xide)                                                                                                                                                                                                                                               |  |

| PL            | Photoluminescence                                                                                                                                                                                                                                                                               |  |

| PMMA          | $\mathbf{P}$ oly(methyl methacrylate)                                                                                                                                                                                                                                                           |  |

| QD            | Quantum $dot$                                                                                                                                                                                                                                                                                   |  |

|               |                                                                                                                                                                                                                                                                                                 |  |

| QPC            | $\mathbf{Q} \mathrm{uantum} \ \mathbf{p} \mathrm{oint} \ \mathbf{c} \mathrm{ontact}$ |

|----------------|--------------------------------------------------------------------------------------|

| SDBS           | Source-drain bias spectroscopy                                                       |

| SEM            | $\mathbf{S} \text{canning } \mathbf{e} \text{lectron } \mathbf{m} \text{icroscope}$  |

| $\mathbf{SMU}$ | Source measure unit                                                                  |

| VB             | Valence Band                                                                         |

| XPS            | ${\bf X}\mbox{-}{\rm ray}\ {\bf p}\mbox{hotoelectron}\ {\bf s}\mbox{pectroscopy}$    |

# **Physical Constants**

| Boltzmann constant         | $k_B$        | = | $1.381 \times 10^{-23} \text{ J/K},$                     |

|----------------------------|--------------|---|----------------------------------------------------------|

| Donzinann constant         |              |   | $8.617\times 10^{-5}~{\rm eV/K}$                         |

| Conductance quantum        | $G_Q$        | = | $\frac{2e^2}{h}$                                         |

| Electron charge            | e            | = | $1.602 \times 10^{-19} \text{ C}$                        |

| Permittivity of free space | $\epsilon_0$ | = | $8.854 \times 10^{-12} \frac{s^4 A^2}{m^3 kg}$           |

| Planck constant            | h            | = | $6.626 \times 10^{-34} \text{ m}^2 \text{kg/s}$          |

| Speed of Light             | c            | = | 2.997 924 58 $\times 10^8 \ {\rm ms}^{-{\rm S}}$ (exact) |

# Symbols

| В                 | Magnetic field                   | tesla [T]                                                            |

|-------------------|----------------------------------|----------------------------------------------------------------------|

| C                 | Capacitance                      | farads [F]                                                           |

| $C_{dot}$         | Quantum dot capacitance          | farads [F]                                                           |

| $C_G$             | Gate capacitance                 | farads [F]                                                           |

| $D_S(E)$          | Density of states at the surface | number of states per square<br>centimetre per eV $[cm^{-2} eV^{-1}]$ |

| $\Delta E_a$      | Quantum dot addition energy      | electron volts [eV]                                                  |

| $E_A, E_D, E_T$   | Acceptor/donor/trap depth        | electron volts [eV]                                                  |

| $E_C, E_V$        | Conduction, Valence band energy  | electron volts [eV]                                                  |

| $E_F$             | Fermi energy                     | electron volts [eV]                                                  |

| $E_g = E_C - E_V$ | Band-gap energy                  | electron volts [eV]                                                  |

| f                 | electrical frequency             | hertz [Hz]                                                           |

| $I_d$             | drain current                    | ampere [A]                                                           |

| $I_G$             | gate leakage current             | ampere [A]                                                           |

| $I_{on}, I_{off}$ | transistor on/off current        | ampere [A]                                                           |

| G                 | conductance                      | siemens [S]                                                          |

| l                 | mean free path                   | metres [m]                                                           |

|                   |                                  | number per cubic centimetre                                          |

| n,p               | electron/hole concentration      | (3D) or square centimetre $(2D)$                                     |

|                   |                                  | $[\rm cm^{-3}]$ or $[\rm cm^{-2}]$                                   |

| Р                 | pressure                         | mbar                                                                 |

| q                 | charge                           | coulombs [C]                                                         |

| R                 | resistance                       | ohms $[\Omega]$                                                      |

|                   |                                  |                                                                      |

|              | S                             | Seebeck coefficient                 | volts per kelvin $[V/K]$             |

|--------------|-------------------------------|-------------------------------------|--------------------------------------|

|              | SS                            | subthreshold swing                  | millivolts per decade $[\rm mV/dec]$ |

|              | T                             | temperature                         | kelvin [K]                           |

|              | $V_G$ or $V_g$                | gate voltage                        | volts [V]                            |

|              | $V_{in}, V_{out}, V_{supply}$ | circuit input/output/supply voltage | volts [V]                            |

|              | $V_{sd}$                      | source-drain voltage                | volts [V]                            |

|              | $V_{th}$                      | threshold voltage                   | volts [V]                            |

|              | $V_T$                         | thermovoltage                       | volts [V]                            |

|              | $V_{PE}$                      | voltage at the PE/NW interface      | volts [V]                            |

|              | $V_{po}$                      | pinch-off voltage                   | volts [V]                            |

|              |                               |                                     |                                      |

| $\epsilon_r$ |                               | dielectric constant/                | unitless                             |

|              | $c_r$                         | relative permittivity               |                                      |

| $\kappa$     |                               | thermal conductivity                | watts per metre kelvin               |

|              | 10                            | onermar conductivity                | $[W/(m{\cdot}K)]$                    |

|              | $\lambda_F$                   | Fermi wavelength                    | nanometre [nm]                       |

|              |                               | charge carrier mobility             | centimetre squared per               |

|              | $\mu$                         | charge carrier mobility             | volt second $[\rm cm^2/Vs]$          |

|              | ν                             | optical frequency                   | hertz [Hz]                           |

|              | Q                             | nanowire radius                     | nanometre [nm]                       |

|              | -                             | aandustivity                        | siemens per centimetre               |

|              | σ                             | conductivity                        | [S/cm]                               |

|              | τ                             | time constant                       | Seconds [s]                          |

|              |                               |                                     |                                      |

## Chapter 1

### Introduction and background

### **1.1** Introduction and chapter outline

The simple concept of the field-effect transistor has had a profound impact on scientific and industrial progress over the last half century through the proliferation of novel devices based on it.<sup>1–9</sup> The underlying field-effect principle is that the flow of electrons through a semiconductor is controlled electrostatically by a gate electrode. From the initial deployment of transistors in amplifiers and then on into switching in computers, the idea of electric fields controlling charge carrier density and tailoring the underlying band-structure has led to the engineering and control of quantum systems,<sup>5–7</sup> and the interfacing of manufactured electronics with biological systems.<sup>10,11</sup> In the meantime, the drive for more efficient technology has driven the size of devices to decrease well beyond many predicted physical limits, with Moore's law driving the exponential decrease in transistor size for five decades. Despite this, there is growing concern that the 7 nm long transistors in development at Intel are finally exposing the limits of silicon as the basis for transistors in integrated circuits. To increase energy efficiency further we need to seek out materials with better performance than silicon, or devices with increased functionality.<sup>4,12</sup>

At the level of fundamental research, substituting new materials and expanding functionality is seldom trivial. The discovery of non-ideal materials properties raises scientific questions that must be solved to fully exploit the new potential advantages. In particular, two chief problems arising as a result of reduction in device size involve dopant impurities and the proximity of the surface to the channel. Size reduction entails a decreasing number of dopant impurities within devices, meaning that non-homogeneous distributions and/or fluctuations in occupation increasingly affect the dynamics of the channel.<sup>13–15</sup> Countering this has involved efforts towards understanding dopant properties and developing strategies to altogether remove dopant impurities.<sup>16–20</sup> Secondly, the increase in surface/volume ratio with size reduction means surfaces increasingly affect device performance.<sup>4,21</sup> The disruption of the ordered crystal structure at surfaces and material interfaces makes them notoriously problematic, with roughness and long-lived charge traps causing mobility reduction and device instability,<sup>4,22–26</sup> along with issues obtaining ideal electrical behaviour of semiconductor/metal interfaces.<sup>27</sup> Once the problems are solved and new functionalities are realised, these devices can be turned back around to study nature, either by embodying a unique system or providing a different way of probing external systems.

My thesis covers this broad spectrum. At one end, we investigated the use of III-V semiconductor materials as the basis for novel transistor devices, including semiconductor nanowires,<sup>28–31</sup> and high-mobility planar heterostructure devices.<sup>32,33</sup> We studied non-ideal behaviours in these systems, including surface/interface charge traps and doping impurities and attempted to develop solutions for them. We also employed new techniques to observe and study these effects. In terms of adding functionality to devices, we explored the manufacture of hybrid organic/inorganic transistors, featuring semiconductor nanowire channels with polymer electrolyte gate dielectrics. This involved characterising the performance advantages of using polymer electrolyte dielectrics, and used them as the basis of an 'external doping' technique to provide a base-line charge carrier density without the need for dopant impurities. The dielectrics could generate quantum systems and also enhance their study at low temperatures in nanowire devices. In addition, we evaluated the thermoelectric properties of these devices, where the ultimate functional goal is conversion of waste heat into electrical energy, or efficiently cooling devices to cryogenic temperatures. Finally, the organic gate allowed us to develop complementary n- and p-type proton-to-electron transducers. These could be used to convert the proton signals typically seen in biological systems into electronic signals that can be read out by conventional electronics.

Chapter 1 gives the background behind my results. I start with the principles of operation of the field-effect transistor (FET), which forms the basis for almost all of the devices studied in this thesis. I then discuss the quantum physics of low-dimensional electron systems and how they can be addressed and controlled through field-effect methods. I discuss novel alternative methods for fabricating transistor elements including self-assembled semiconductor nanowires and polymer electrolyte gates. I also outline the non-ideal behaviours in research level devices that we seek to optimise, and explore the concept of biological interfacing.

Chapter 2 outlines the experimental procedures used in this thesis. This includes device fabrication and electrical measurement techniques at room temperature and low temperature,  $T \leq 4.2$  K.

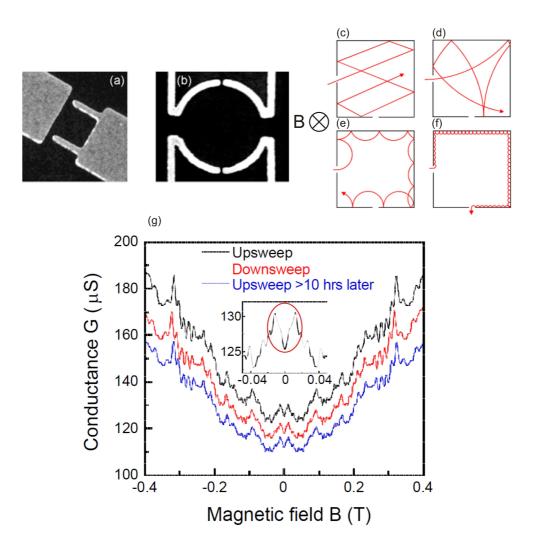

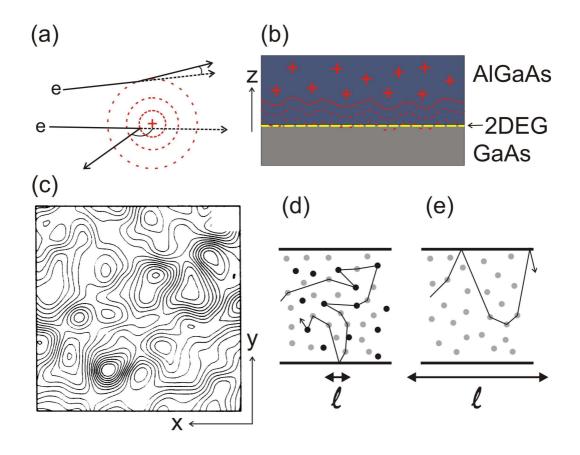

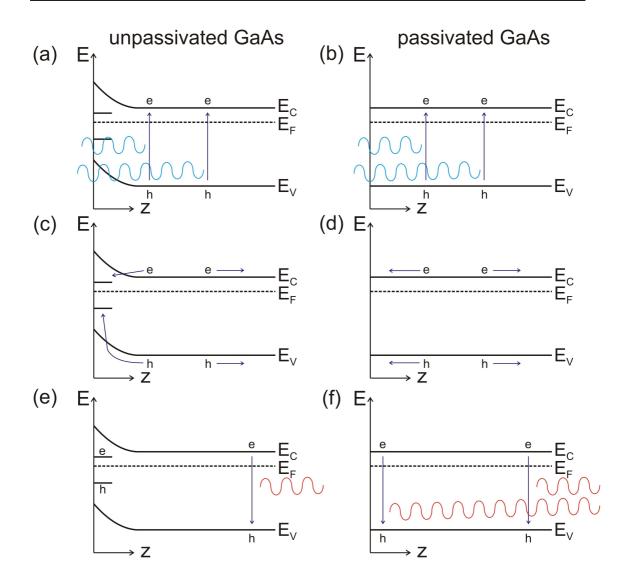

Chapter 3 presents results on the cause of instability in *p*-type GaAs/AlGaAs heterostructures. High electron mobility *n*-type GaAs/AlGaAs heterostructures have formed the basis for a wealth of low dimensional quantum systems, but making the same kind of systems with holes in *p*-type heterostructures has been inhibited by gate instability. We explored the effect of surface states and dopant impurity charge migration on the operation of devices made from these structures. We attempted passivation of the (311)-oriented surface used for *p*-type heterostructures, and found why typical treatments were not as effective as for the more common (100)-oriented surface. We also fabricated a hole quantum dot in this material and used the unique signature of conductance fluctuations in response to an external magnetic field to capture a 'fingerprint' of changes in dopant impurity distributions. Chapter 4 focusses on novel techniques for gating self-assembled semiconductor nanowires. The results centre on gates that wrap around the nanowire to give the best control. We fabricated devices with multiple gates, using both traditional metal/oxide structures as well as polymer electrolyte gate dielectrics. In the latter case we developed a method to nanoscale pattern poly(ethylene oxide)-based polymer electrolytes and showed this organic/inorganic combination enhanced the functionality of both materials systems.

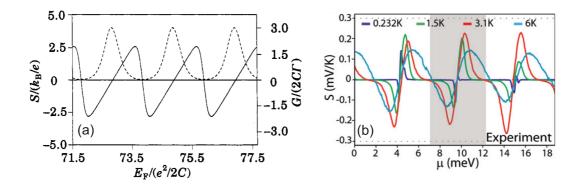

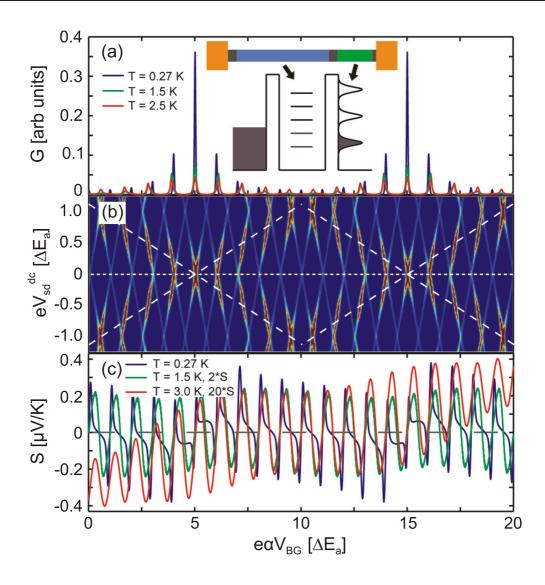

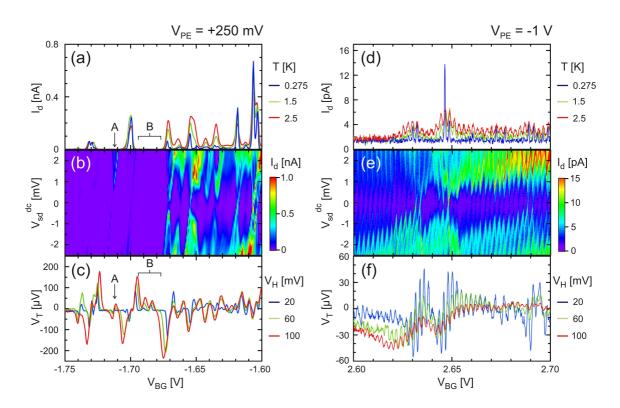

Chapter 5 explores the use of polymer electrolyte gates to enhance quantum systems in nanowires. The polymer electrolyte gates were used to 'set and freeze' the base-line charge density and the background potential for electrons traversing the nanowire at  $T \leq 4.2$  K. To help probe this system we used thermoelectric measurements, which can give additional information to complement traditional conductance measurements. In doing so we also showed that polymer electrolytes could play a vital role in thermoelectric cooling applications that require a specific charge density be set.

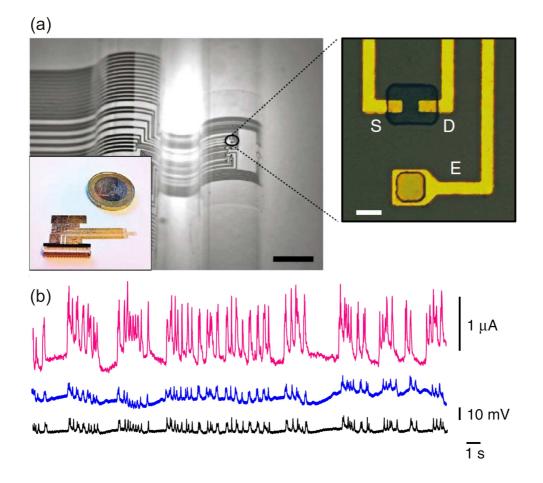

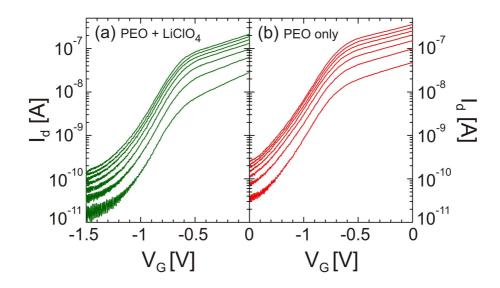

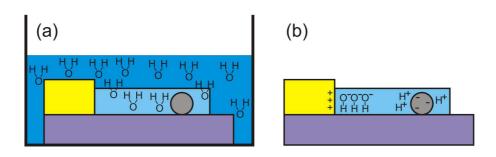

Chapter 6 explores the use nanoscale poly(ethylene oxide) dielectrics to facilitate proof-of-principle measurements for integrating nanowires with nano-biology. We discovered that these dielectrics supported proton transport and characterised the proton dynamics as a function of hydration level using nanowire transistors. This revealed a relatively high conductivity for protons in poly(ethylene oxide). The importance is that signalling in many biological systems occurs *via* proton transport rather than electron transport. As a result, interfacing manufactured electronics with the biological world requires transduction of these proton signals into electrical signals. Using *n*-InAs and *p*-GaAs nanowire channels, we fabricated complementary nanowire transistors gated by the field-effect arising from local proton concentration. The result was that a change in current caused by proton concentration fluctuations could be read out electronically. Pairing *n*-InAs and *p*-GaAs nanowires devices in functional circuits may open the possibility for size appropriate amplifiers of biological signals on chips compatible with Si-based microelectronics. Chapter 7 rounds out my thesis by summarising the key results and suggesting future directions. Using the examples from this thesis I show that the scientific study of device physics sits neatly between the motivations of understanding constituent material properties and the desire to generate novel devices that facilitate new understandings of physical systems from quantum to biological.

### **1.2** The field-effect transistor

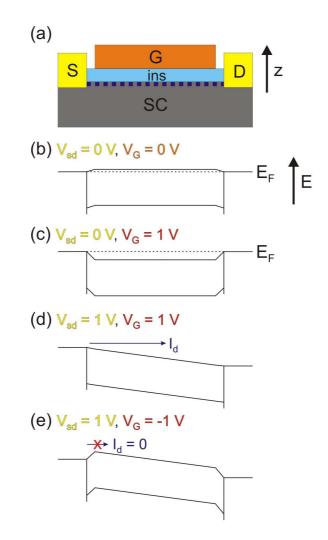

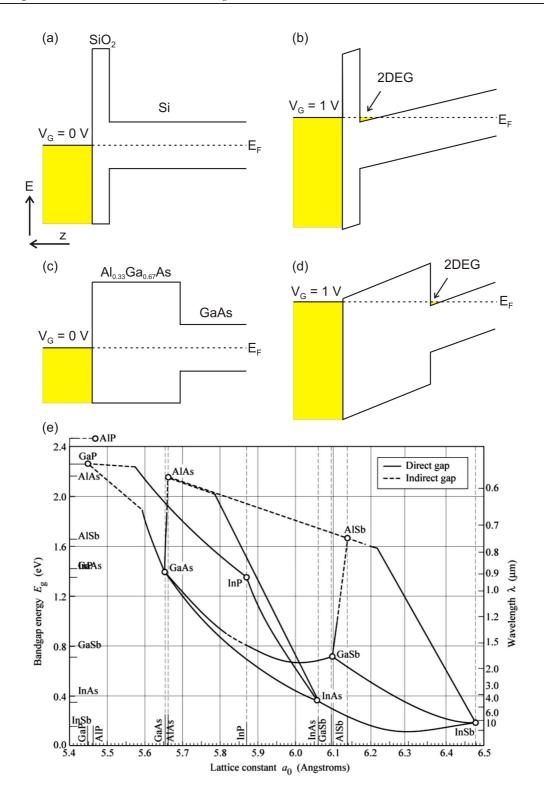

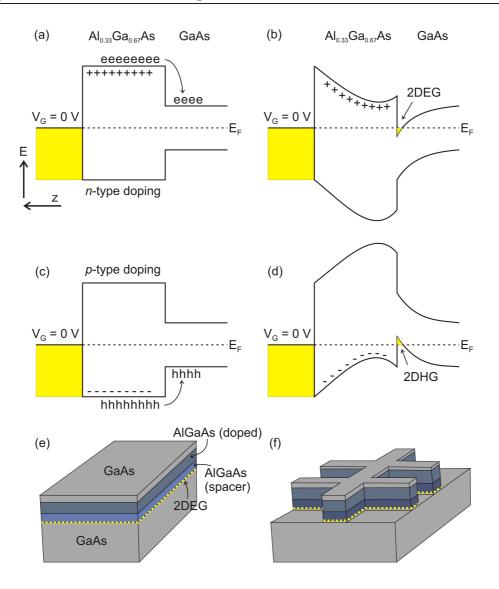

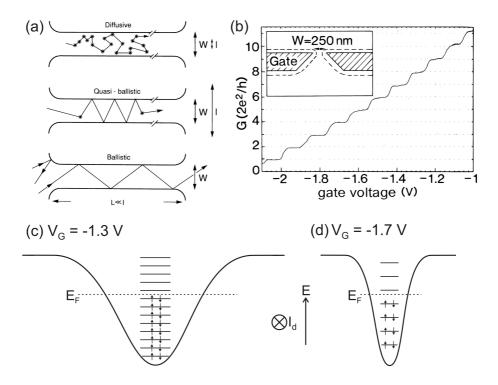

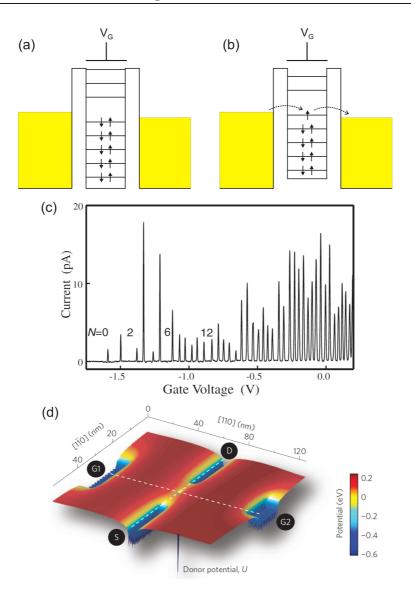

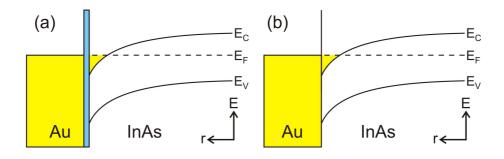

The field-effect transistor (FET) consists of a semiconductor channel, usually doped *n*- or *p*-type, and three metal electrodes (see Fig. 1.1(a)). Device behaviour is determined by the different effect that voltages on these electrodes have on the bands and Fermi level within the semiconductor. The source and drain are electrically connected to the channel. Ideally the contacts are 'ohmic' – i.e. obey Ohm's law V = RI – with a low resistance such that the source/drain voltage  $V_{sd}$  drops mostly across the semiconductor channel (Fig. 1.1(b)). The contact between metals and semiconductors typically results in a potential barrier known as a Schottky barrier. This can be overcome by including a dopant in the contact metal and diffusing it into the semiconductor to form a thin, highly doped layer below the contact. The gate electrode is electrically insulated from the semiconductor; when an oxide layer is used, these devices are known as metal-oxide-semiconductor FETs (MOSFETs). Applying a voltage  $V_G$  to the gate capacitively depletes or induces charge carriers in the conduction channel. In energetic terms,  $V_G$  and the associated electric field alter the energy of the conduction and valence bands with respect to the Fermi level  $E_F$ , illustrated in Fig. 1.1(c). To pass a current  $I_d$ through the channel,  $V_{sd}$  is applied between source and drain to drive the device out of equilibrium, as in Fig. 1.1(d). In this way, the combination of  $V_{sd}$  and  $V_G$ determines the potential landscape for electrons/holes traversing the semiconductor channel, e.g. Fig. 1.1(e) illustrates how the gate is used to generate a potential barrier that stops the flow of current.

FIGURE 1.1: (a) Schematic of a field-effect transistor featuring metallic source (S), drain (D) and gate (G) electrodes along with the semiconductor channel (SC) and gate insulator (ins). The conduction channel is illustrated with the purple dotted line. (b) Band diagram of the device in (a) for  $V_{sd} = V_G = 0$  V. The source and drain have formed ohmic contacts with the semiconductor as the conduction band is aligned with the Fermi level  $E_F$  at S and D. (c) Positive applied  $V_G$  moves the position of the bands relative to  $E_F$ , increasing electron density. (d) An applied  $V_{sd}$  allows current  $I_d$  to flow through the device. (e)  $I_d$  is turned off by a negative  $V_G$ , as it causes a potential barrier for electrons.

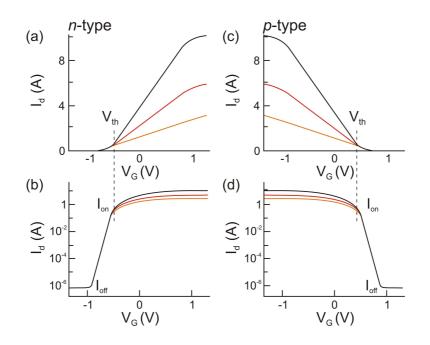

Figure 1.2 shows the idealised  $I_d$  response to  $V_G$  applied to *n*- and *p*-type transistors at different  $V_{sd}$ . These plots are known as 'transfer characteristics'. More positive/negative  $V_G$  increases/depletes the electron/hole density, increasing/decreasing channel conduction; the device is said to be 'on'. Supplying a larger  $V_{sd}$  results in increased  $I_d$  for each  $V_G$ . Reversing the  $V_G$  direction depletes carriers.

FIGURE 1.2: Transfer characteristics for n- and p-type transistors (a/b and c/d respectively) with linear and log  $I_d$  axes (top and bottom). The black, red and orange traces represent decreasing, constant  $V_{sd}$ . Below  $V_{th}$ ,  $I_d$  drops exponentially from  $I_{on}$  to  $I_{off}$ .

At the threshold voltage  $V_{th}$  the band diagram looks like Fig. 1.1(e), where a potential barrier blocks transport. Here,  $V_{sd}$  has no effect on  $I_d$  as the barrier height depends only on  $V_G$ . The current through the device goes to zero exponentially with  $V_G$ , turning off the device. The exponential turn-off in the subthreshold region can be seen more easily on a log-linear plot (Figs 1.2(b/d)), where  $\log(I_d)$  vs.  $V_G$  has a linear slope. The inverse subthreshold slope is called the subthreshold swing  $SS \equiv \frac{\partial V_G}{\partial \log(I_d)}$ , given in mV of  $V_G$  per decade change of  $I_d$ , i.e. mV/dec. It is an important metric as it quantifies the  $V_G$  swing required to turn the device off; a low SS is vital for low power applications. The value is determined by material parameters and energy considerations, and is thermodynamically limited to around 60 mV/dec at room temperature.<sup>1</sup> A good transistor combines a low SSwith a high on/off ratio,  $\frac{I_{onf}}{I_{off}}$ . This results in orders of magnitude changes in device resistance within a 1 V range of  $V_G$ . The next section discusses the importance of these features for switching and amplification.

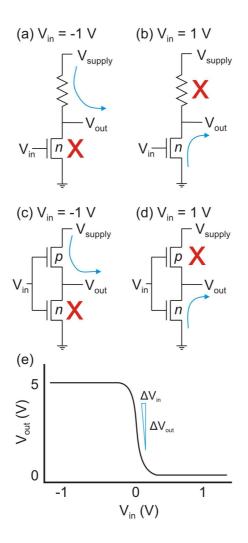

FIGURE 1.3: (a/b) An *n*MOS inverter circuit with *n*-type transistor and series resistor. (a) For  $V_{in} = -1$  V, the transistor is off, and  $V_{out} = V_{supply}$ . (b) For  $V_{in} = 1$  V, the transistor is on, making  $V_{out} = 0$  V. (c/d) a CMOS inverter with *p*- and *n*-type transistors. The  $V_{in}$  swing between -1 and 1 V takes the *p*-type/*n*-type devices from off/on to on/off, respectively. (e)  $V_{out}$  vs.  $V_{in}$  for a well matched CMOS inverter. The steep slope around  $V_{in} = 0$  V facilitates small signal amplification with high gain  $\Delta V_{out}/\Delta V_{in}$ .

#### **1.2.1** Basic applications: switching and amplification

Two examples of an inverter are shown in Fig. 1.3. This is the most basic circuit for transistor switching and amplification. In the first example (Figs 1.3(a/b)), a resistor is placed in series with the *n*-transistor channel, and  $V_{supply} = 5$  V is applied across the resistor and channel. A signal  $V_{in}$  is applied to the gate, and the response  $V_{out}$  is read out between the resistor and transistor source. Typical transistor ON and OFF resistances  $R_T$  are in the k $\Omega$  and G $\Omega$  ranges, respectively. The resistor value  $R_R$  is chosen to be between the ON and OFF resistances, e.g.,  $R_R = 1 \text{ M}\Omega$ . For  $V_{in} = -1 \text{ V}$ , the transistor is off, and since  $R_R \ll R_T$  by orders of magnitude, the  $V_{out}$  is linked to the  $V_{supply} = 5 \text{ V}$ . When the input is reversed to  $V_{in} = 1 \text{ V}$ ,  $R_R \gg R_T$ ; this essentially grounds  $V_{out} = 0 \text{ V}$  through the open transistor channel. In this way, switching  $V_{in}$  between two voltages switches  $V_{out}$ also. In addition, the 2 V signal (from -1 to +1 V) at  $V_{in}$  is amplified to a 5 V signal at  $V_{out}$ . The fact that a high  $V_{in}$  gave a low  $V_{out}$  and vice versa is the origin of the term 'inverter'.

Inverter performance is improved by using complementary *n*-type and *p*-type MOSFETs in the configuration of Figs 1.3(c/d). This is the cornerstone of the complementary MOS (CMOS) platform that is the basis for computer processor technology. A CMOS inverter simply replaces the resistor from the circuit in Figs 1.3(a/b) with a *p*-type transistor, and  $V_{in}$  is applied to both gates simultaneously. Here,  $V_{in} = -1$  V turns the *p*-transistor on and the *n*-transistor off, giving  $V_{out} = 5$  V. Similarly,  $V_{in} = 1$  V turns the *p*-transistor off and the *n*-transistor on, giving  $V_{out} = 0$  V. High amplification gain is achieved by applying small signals around the point where  $V_{in}$  swings  $V_{out}$  between  $V_{supply}$  and ground. Figure 1.3(e) shows that at this point very small changes in  $V_{in}$  result in large changes in  $V_{out}$ ; the origin of the voltage gain.

The switching action of inverters also gives a practical realisation of the NOT logic operation, since high voltages (logic state 1) on the input map to low voltages (logic state 0) on the output and vice versa. CMOS is used in computer processor technology due to its low power consumption: when  $V_{in} = \pm 1$  V, one or the other of the transistor channels is closed and no current flows through the circuit. This means power is only consumed very briefly during switching events.<sup>2</sup> More complex CMOS configurations yield practical realisations of logic operations such as AND and OR. However, demonstration of an inverter is typically at the edge of fundamental research as it serves as a proof-of-principle for a new potential CMOS platform. Scaling up the platform and optimising integrated circuits is mostly an engineering problem from that point onwards.

### **1.3** Non-ideal properties of real devices

The band structure of solid state materials arises from the regularity of atomic placement in a crystal lattice: the overlapping atomic orbitals hybridise to form energy bands that span the entire crystal.<sup>34</sup> While modern growth techniques such as molecular beam epitaxy have allowed manufacture of near perfect crystals with atomic precision,<sup>35</sup> the majority of materials contain imperfections and impurities. Indeed, the doping of semiconductors entails intentionally introducing impurities. Further, the crystal structure necessarily breaks down dramatically at the surface, or at interfaces with other materials.<sup>34</sup> Below I will briefly discuss how these defects can be understood as localised perturbations against the backdrop of the non-localised bands, and how the down-sizing of devices places increased importance on the distribution of dopant atoms and the effects of surfaces.

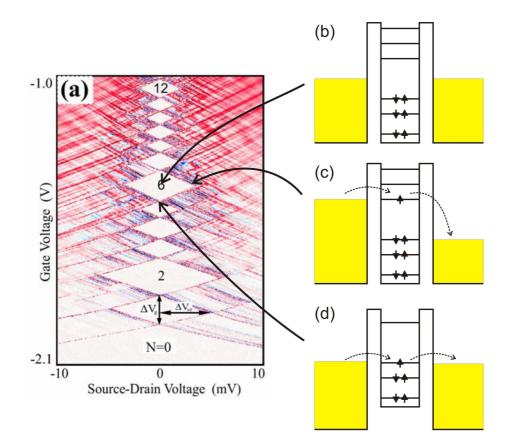

#### 1.3.1 Doping and bulk impurities

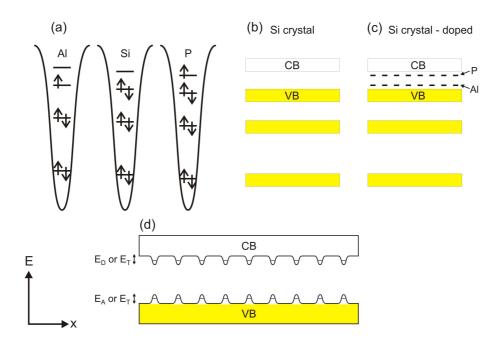

The most familiar microscopic modification to a band structure arises from doping impurities. A comparatively low concentration of atoms with one more or less proton than that of the host crystal is introduced.<sup>34</sup> Figure 1.4 illustrates how the atomic orbitals of the dopant atoms do not overlap like those of the host crystal. Hence they do not form a continuous band; rather their energy levels remain localised at the physical location of each dopant. For higher proton number Z, the attraction to the nucleus is stronger, giving more tightly bound atomic energy levels. This means that for, e.g., P in Si (Z = 29 and 28 respectively), isolated energy levels containing an electron sit just below the conduction band. If the difference in energy between the dopant level and conduction band is small compared to the thermal energy  $k_BT$ , the electrons will populate the conduction band and leave behind ionised dopant impurities. Similarly, the energy levels of Al are shifted slightly higher than Si, providing a localised empty energy state above the valence band. This traps electrons and leaves a non-localised hole in the valence band.

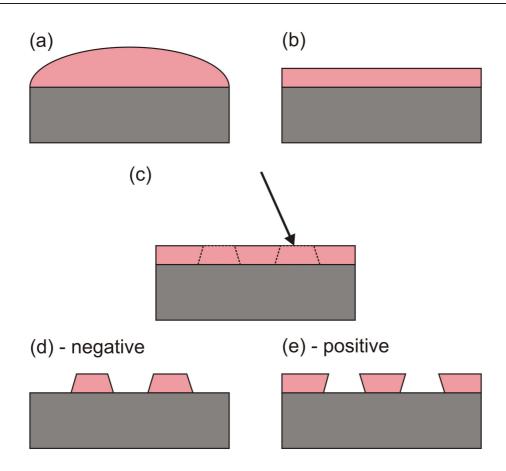

FIGURE 1.4: (a) Energy spectrum for isolated aluminium, silicon and phosphorous atoms. Increasing Z results in an additional electron (represented by spin arrows), and also generates a stronger attractive force, pulling energy levels down. (b) Hybridisation of discrete atomic orbitals leads to the formation of bands. In semiconductors, the bands are occupied until the top of the valence band (VB), leaving and empty conduction band (CB). A small density of Al or P impurities in the Si crystal act as if they are isolated atoms with discrete energy levels. (d) Impurity incorporation modifies the bands to add potential wells for electrons in the CB and holes in the VB. The wells can act as charge traps if the donor/acceptor/trap depth exceeds thermal energy,  $E_D, E_A, E_T > k_BT$ .

The incorporation of unintentional impurities is conceptually no different; the result is localised discrete energy levels dispersed throughout the crystal. Both unintentional and intentional impurities can possess undesirable features that contribute negatively to device performance. Since they provide potential wells just below/above the conduction/valence bands (Fig. 1.4(d)), impurities can act as electron/hole traps if the well depth  $E_T$  is large compared to  $k_BT$ . Here, a free electron trapped in the deep well is unable to escape due to insufficient thermal energy. If the trap depth  $E_T \sim k_BT$ , the charge state of the impurity may fluctuate between positive (unoccupied) and neutral (occupied) as electrons enter and leave the trap spontaneously. In larger devices the effect of many impurities rapidly switching charge state may be averaged out and not affect operation. By contrast, nm-scale devices often exist on the scale of the potential generated by the

FIGURE 1.5: Data from an experiment by Pioro-Ladrière *et al.*<sup>15</sup> The main figure shows conductance  $G = \frac{I_d}{V_{sd}}$  vs. gate voltage  $V_g$  for the device shown in the lower inset. The device consists of split surface gates that generate a 1D quantum system in an underlying AlGaAs/GaAs heterostructure as described in Section 1.4.2. The data is noisy due to a two-level switching behaviour arising as a result of changing occupation of nearby Si dopant impurities. Upper inset: The two-level switching is clearly seen if the device is held at constant  $V_g \sim -0.64$  V, marked with a cross in the main figure.

impurity.<sup>13,14,36</sup> Such devices can be greatly affected if this potential switches between charge states. For instance, the current through a sensitive quantum device in Fig. 1.5 switches between two states as a nearby single impurity charges and discharges.<sup>15,37</sup> The importance of impurity configuration in setting a background potential for quantum devices is only now being fully appreciated; I will discuss this in Section 1.4.4 and present results from a device where background impurities dominate device behaviour in Chapter 3.

### **1.3.2** Surface states and interface states

The most dramatic rupture of the crystal structure comes at the surface. The ordered lattice structure is abruptly terminated, leaving surface atoms with unsatisfied dangling bonds, as in Fig. 1.6(a).<sup>2,21,34,39</sup> The dangling bonds seek to form surface bonds with each other as in Fig. 1.6(b), or capture oxygen atoms from the atmosphere and form a thin, amorphous oxide layer. Each of these surface bonds

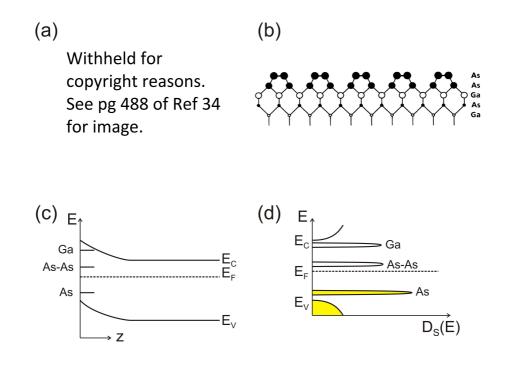

FIGURE 1.6: (a) The underlying order of a crystal is disrupted at the surface, leaving surface atoms with unsatisfied dangling bonds. (b) One possible reconstruction the (100) GaAs surface may take in order to satisfy dangling bonds, according to Ref. 38. The surface of semiconductors exposed to air consists of an amorphous layer of oxides. (c) Band diagram near the (100) surface of *n*-type GaAs. The Ga-dangling, As-dangling and As-As dimer bonds generate surface states that pin  $E_F$  mid-gap, but the doping level requires  $E_F$  to sit closer to  $E_C$  in the bulk. This generates a surface barrier that makes it difficult to inject carriers. (d) Density of states at the surface  $D_{SS}(E)$  illustrating the source of  $E_F$  pinning. The high density of surface states compared to conduction and valence band states means surface state occupation/density determines the Fermi level position. Note this diagram only applies at the semiconductor surface due to the localised nature of the surface states. Images in (a) and (b) from Refs 34 and 38.

are different to the bulk lattice bonds, and as such their associated electron energy states do not necessarily correspond to energies within the bulk bands. If the energies exist in the bulk band gap, these so called 'surface states' act as deep trapping sites localised at the surface.<sup>21,39</sup> Taking GaAs as an example, Fig. 1.6(c) shows that a clean (100) surface in vacuum consists of: Ga-dangling bonds associated with empty surface states; filled As- dangling bonds associated with filled states; and in some cases, As-As dimers associated with empty mid-gap surface states.<sup>21,40–43</sup> The surface states with energies in the band gap act as deep charge traps. By comparison, InAs has a smaller band-gap (0.345 eV vs. 1.42 eV for GaAs) and so the highest density of surface states is in the conduction band.<sup>40</sup> In reality this surface state spectrum is modified following exposure to air due to the growth of an amorphous native oxide layer.<sup>44,45</sup>

A high density of surface states presents numerous problems when depositing metal onto a semiconductor to act as source/drain contacts or gates. The problems arise from Fermi level position being determined by the occupation of these surface states, rather than the occupation in the bulk energy bands (see Fig. 1.6(d)). This pins the Fermi level of any metal deposited on the surface with limited dependence on metal composition and semiconductor doping concentration.<sup>27,46,47</sup> For GaAs, the Fermi level is pinned mid-gap, making it difficult to inject carriers into the conduction or valence band. For InAs, the Fermi level pinning in the conduction band.<sup>48</sup> Both situations are far from the ideal whereby the interface Schottky barrier can be tuned by metal composition and semiconductor doping.<sup>2</sup>

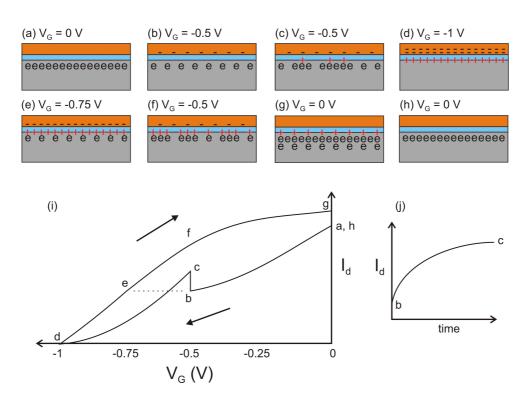

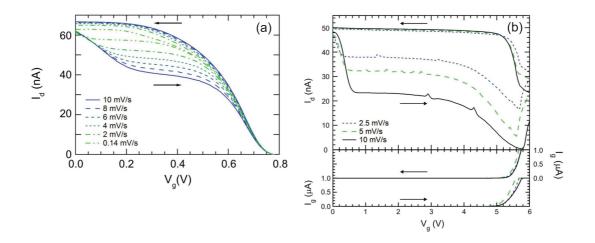

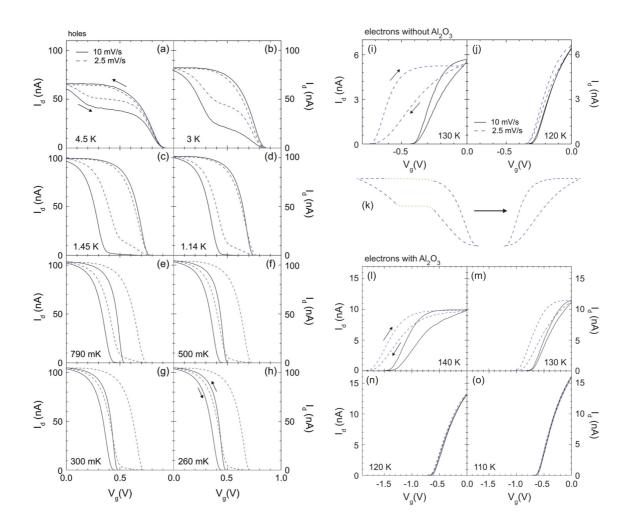

If the surface states are deep, long-lived traps (i.e.  $E_T > k_B T$ ) with a high density, they can cause instability and hysteresis when gating transistors. This is outlined in Fig. 1.7 for an *n*-type channel. A negative voltage on the gate may cause positive charge to be trapped in the surface states at the expense of depleting the channel underneath. This reduces the ability of the gate to deplete the channel, and in extreme cases may result in regions where  $I_d$  is not affected by  $V_G$  at all, as all of the energy goes into populating surface states. If a sweep to depletion is stopped,  $I_d$  will rise over time as the charge traps continue to be filled with positive charge that compensates the gate voltage. Once all the charge traps are filled, the Fermi level can be controlled again and depletion can continue. As the gate is swept towards zero, the charge traps will depopulate, but depopulate slowly. This means that initially the gate has good control over the channel, and  $I_d$  rises quickly, following a higher path than it did on the sweep to depletion. This produces the clockwise hysteresis loop for electron devices in Fig. 1.7. The characteristics for hole devices is the mirror image, since depletion occurs for positive voltages. This produces an anti-clockwise hysteresis loop that will be important in discussion of instability in *p*-type quantum devices in Sec. 1.4.5 and Chapter 3.

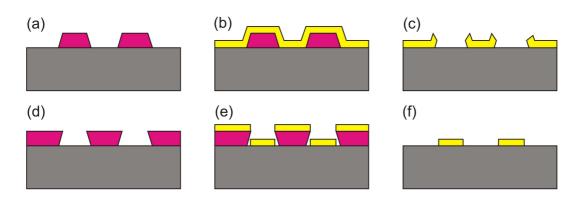

FIGURE 1.7: (a-h) Illustration of surface state charge trapping in a MOS-FET with metal gate (orange), insulator (blue) and semiconductor channel (grey).(i/j) Electrical characteristics corresponding to how each situation in (ah) generates hysteresis and instability in device characteristics. (a) Electrons, e, in the semiconductor channel carry current  $I_d$ . (b) Increasing  $V_G$  applies negative charge to the gate (-), depleting the channel of electrons. (c) Holding  $V_G = -0.5$  V causes trapping of positive charges at the semiconductor/oxide interface (+), leading to the re-accumulation of electrons. (d) The channel is fully depleted at  $V_G = -1$  V, but depletion may have required filling of all surface states. (e) As  $V_G \rightarrow 0$  V, the surface states de-trap slowly. As such, the electron density for  $V_G = -0.75$  V on this sweep is the same as it was for  $V_G = -0.5$  on the sweep towards  $V_G = 1$  V. (f) Similarly, the electron density for  $V_G = -0.5$  V on this sweep is higher than it was for  $V_G = -0.5$  on the sweep towards  $V_G = 1$  V. (g) Not all surface states have de-trapped at  $V_G = 0$  V, giving a higher current than in (a). (h) With time, surface states may de-trap, returning the device to the state it was at (a). (i) Hysteretic  $I_d$  vs.  $V_G$  traces for the sweeps to and from  $V_G = -1$  V. Points corresponding to figures (a-h) are indicated. The dashed line shows that  $I_d$  is the same at points b and e. (j)  $I_d$ increases over time from points b to c as surface traps fill slowly, compensating the gate voltage at constant  $V_G = -0.5$  V.

#### **1.3.2.1** Surface state passivation

The success of Si-based transistors has much to do with the fact that the bonds between Si and its native oxide  $SiO_2$  result in a low density of band-gap surface

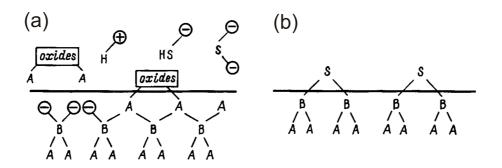

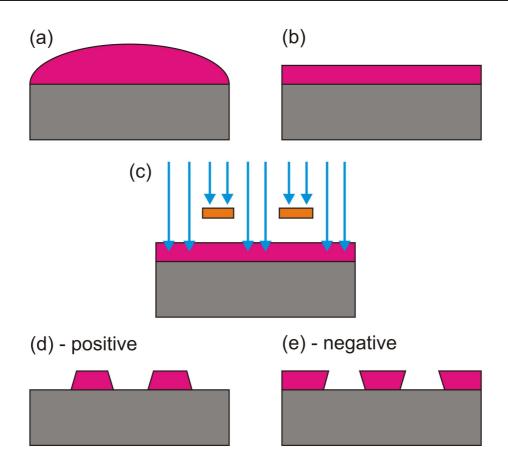

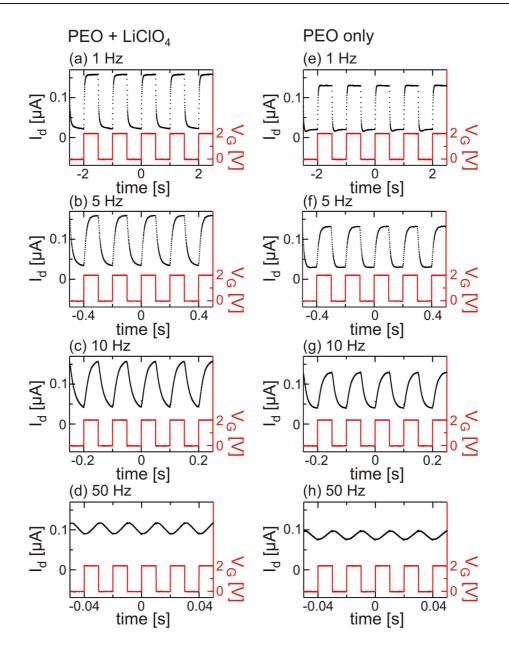

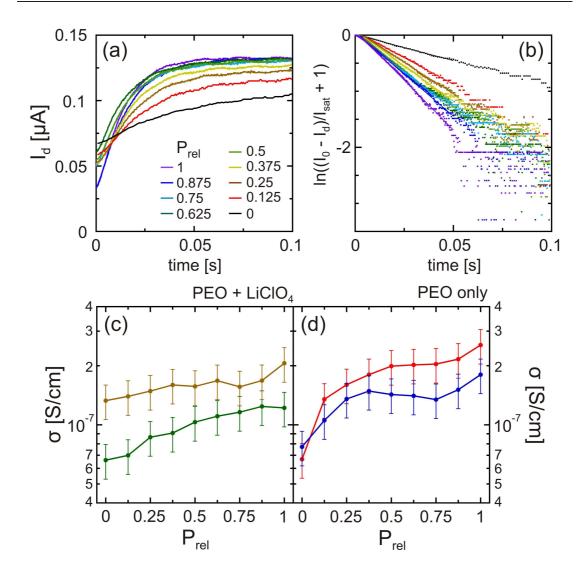

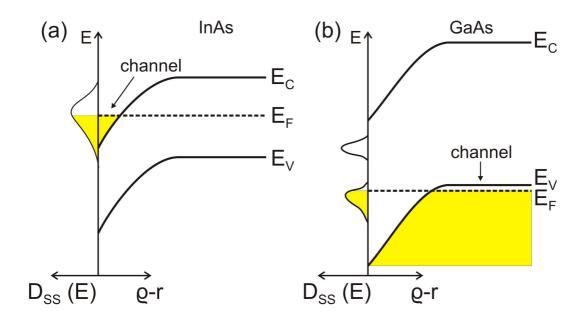

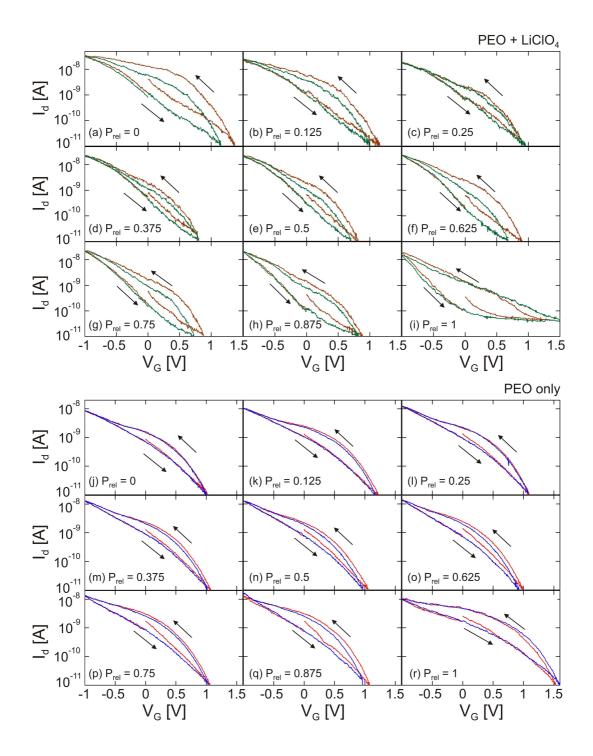

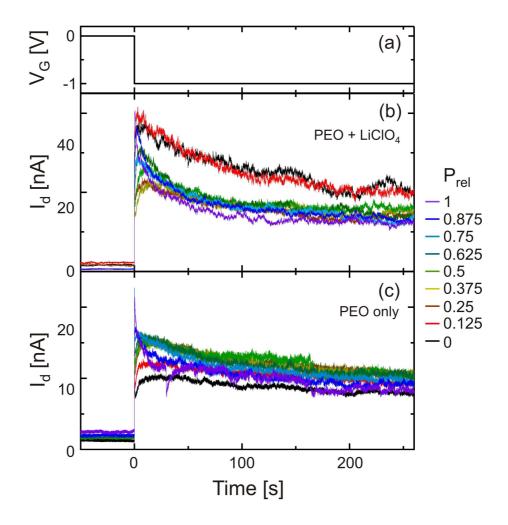

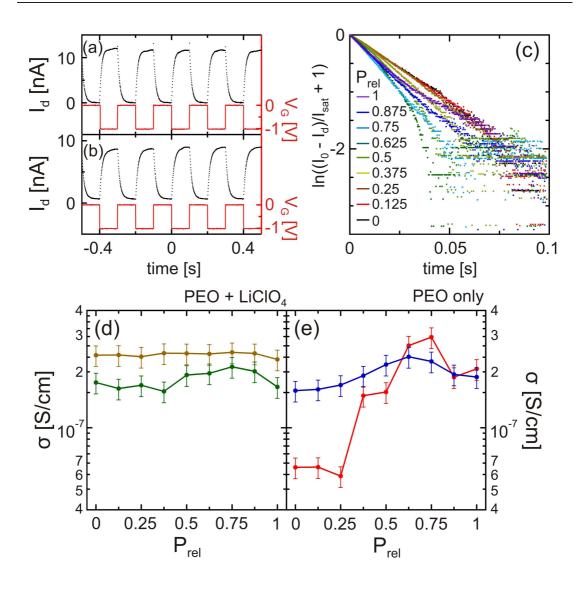

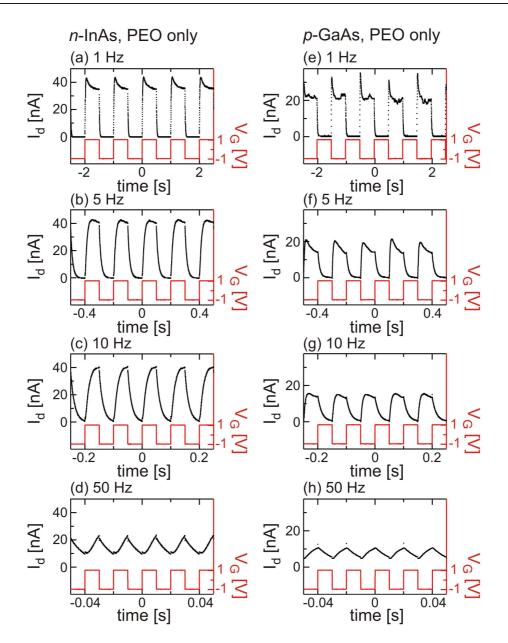

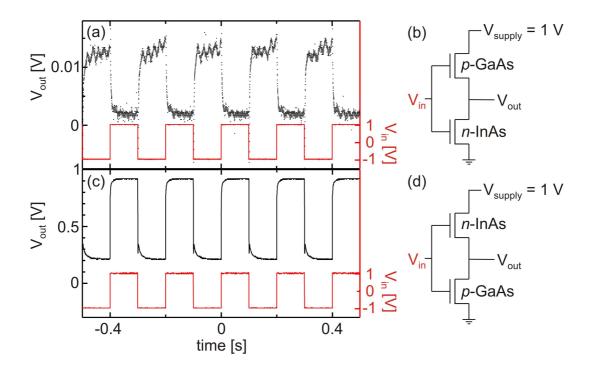

FIGURE 1.8: Chemical passivation for III-V semiconductors. A and B represent group-III and group-V elements, respectively. (a) The alkali solution etches the surface oxide layer. (b) Sulfur atoms form surface bonds, ideally with energy states outside the band gap. Adapted from Ref. 44.