# A gateway between XLNET and TMS-IBM token ring

**Author:** Wang, Yi-Chun

**Publication Date:** 1990

DOI: https://doi.org/10.26190/unsworks/10165

# License:

https://creativecommons.org/licenses/by-nc-nd/3.0/au/ Link to license to see what you are allowed to do with this resource.

Downloaded from http://hdl.handle.net/1959.4/65128 in https:// unsworks.unsw.edu.au on 2024-04-30

# A Gateway between XLNET and TMS-IBM Token Ring

A Thesis

### Submitted to the University of New South Wales

Kensington, New South Wales, Australia

as

Requirement for the Degree of

Master of Engineering

by

Yi-Chun Wang

June, 1990

UNIVERSITY OF N.S.W.

10 MAY 1991

LIBRARY

I hereby declare that this thesis is my own work and that, to the best of my knowledge and belief, it contains no material previously published or written by another person nor material which to a substantial extent has been accepted for the award of any other degree or diploma of a university or other institute of higher learning, except where due acknowledgement is made in the text of the thesis.

Signed

#### ACKNOWLEDGEMENTS

The research program reported here was carried out in the Department of Communication of University of New South Wales under the supervision of Professor A.E. Karbowiak and Associate Professor P.L. Chu. I would like to express my appreciation and thanks for their guidance and encouragement throughout the project.

I am also grateful to the pleasant working atmosphere created by my friends, Paulos Nyirenda, Weiming Li and Rhonda Chuang. Special mention goes to Hassan Mehrpour, Frank Lui and Thomas Fong for their valuable assistance and advice in this project.

Finally, I would like to express my profound thanks to my parents for their loving support and understanding over the past two years; without them this work would never have been possible.

#### ABSTRACT

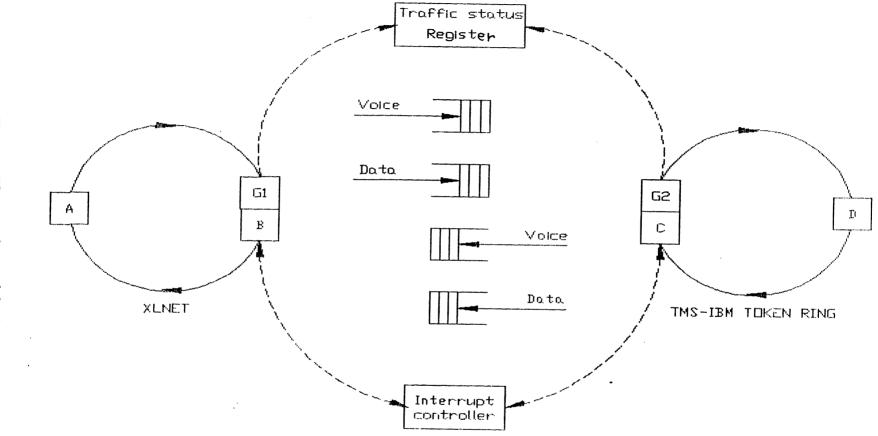

The difficulty of interconnecting networks when they obey different architectures is an important inhibitor to computer communication growth and flexibility. Therefore, a suitable link device must be required to solve interconnection problems of dissimilar networks. The aim of this thesis is to perform a theoretical and experimental investigation on a linking device (gateway) employed in the two heterogeneous local area networks (LANs), XLNET and TMS-IBM Token Ring.

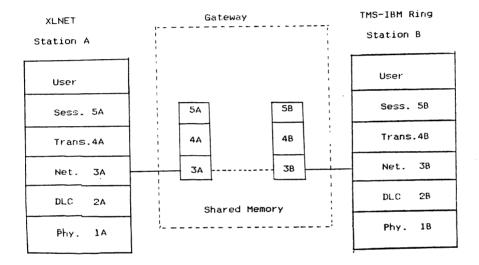

To do this, we first review some important aspects of the two LANs considered to be connected. These two LANs have dissimilar layer protocols we find up to the Session Layer. In our research, neither a bridge nor X.75 protocol would be a suitable communicator, except that a gateway provided with the function of protocol conversion, is able to achieve the peer-to-peer communication in this interconnecting system. Therefore, the gateway is employed in our project. Moreover, by the shared memory scheme installed at the Network Layer of a gateway, we can limit the protocol conversion just to the Transport Layer and Session Layer. By this means, the cost on the conversion in the rest of layers is saved and the speed of the internet packets transmission can be increased.

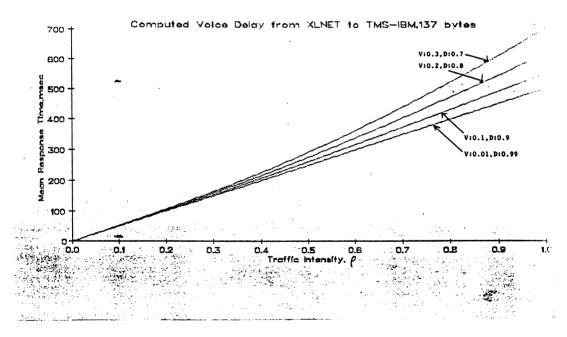

The design of the gateway including hardware and software is presented in this thesis. Furthermore, the performance of the gateway are analyzed. A simplified queueing model is adopted to yield approximate expressions for the mean delay time and throughput. The laboratory results are compared with the computed ones, and close agreement is observed.

# CONTENTS

### ACKNOWLEDGEMENTS

## ABSTRACT

| Chapter 1. | Introduction                                 |    |  |  |

|------------|----------------------------------------------|----|--|--|

| 1.1        | The Need for a Gateway                       | 1  |  |  |

| 1.2        | The OSI Model                                | 4  |  |  |

| 1.3        | Structure of the Thesis                      | 7  |  |  |

| Chapter 2. | Overview of XLNET                            |    |  |  |

| 2.1        | Introduction                                 | 10 |  |  |

| 2.2        | Hardware Aspects                             |    |  |  |

| 2.3        | Software Aspects                             | 12 |  |  |

| 2.4        | Other Significant Features                   | 17 |  |  |

|            | 2.4.1 Strategy of Token Generation           | 19 |  |  |

|            | 2.4.2 Distributed Cycle Service Scheme       | 21 |  |  |

|            | 2.4.3 Efficient Improvement on Voice Service | 24 |  |  |

|            | 2.4.4 Speech Interpolation and its Advantage | 26 |  |  |

| Chapter 3. | Overview of TMS-IBM Token Ring               |    |  |  |

| 3.1        | Introduction                                 | 29 |  |  |

| 3.2        | Hardware AspectsTMS-380 Adapter Chipset      |    |  |  |

|            | 3.2.1 TMS38010 Communication Processor (CP)  | 31 |  |  |

|            | 3.2.2 TMS38020 Protocol Handler (PH)         | 31 |  |  |

|            | 3.2.3 TMS38030 System Interface (SIF)        | 32 |  |  |

| 3.2.4 TMS38051 Ring Interface Transceiver (RIT) |                                              |    |  |  |  |

|-------------------------------------------------|----------------------------------------------|----|--|--|--|

|                                                 | and TMS38052 Ring Interface Controller (RIC) | 32 |  |  |  |

|                                                 | 3.2.5 The Operation of the TMS-380 Adapter   | 32 |  |  |  |

| 3.3                                             | Description of Software                      | 36 |  |  |  |

| 3.4                                             | Special Features                             | 38 |  |  |  |

|                                                 | 3.4.1 The Integration Service                | 38 |  |  |  |

|                                                 | 3.4.2 The Scheme of Speech Interpolation     | 40 |  |  |  |

|                                                 | 3.4.3 Token Access Technology                | 40 |  |  |  |

| Chapter 4.                                      | Resolution of Architectural Issues           | 44 |  |  |  |

| 4.1                                             | Introduction                                 | 44 |  |  |  |

| 4.2                                             | Subnet Independence                          | 45 |  |  |  |

| 4.3                                             | Internetwork Architectures                   | 47 |  |  |  |

|                                                 | 4.3.1 Bridge                                 | 50 |  |  |  |

|                                                 | 4.3.2 X.75                                   | 52 |  |  |  |

|                                                 | 4.3.3 Internet Protocol (IP)                 | 53 |  |  |  |

|                                                 | 4.3.4 Protocol Translator                    | 60 |  |  |  |

|                                                 | 4.3.4.1 Shared Memory Scheme                 | 63 |  |  |  |

| 4.4                                             | Communication Services                       | 66 |  |  |  |

| 4.5                                             | Addressing                                   | 69 |  |  |  |

| 4.6                                             | Segmentation and Reassembly                  | 71 |  |  |  |

| . 4.7                                           | Routing                                      | 73 |  |  |  |

| Chapter 5.                                      | Laboratory Implementation                    |    |  |  |  |

| 5.1                                             | Introduction                                 | 74 |  |  |  |

| 5.2                                             | Overview of the Experimental Gateway         | 74 |  |  |  |

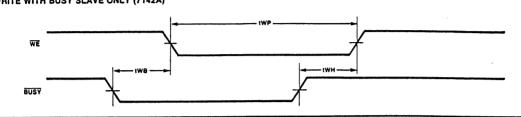

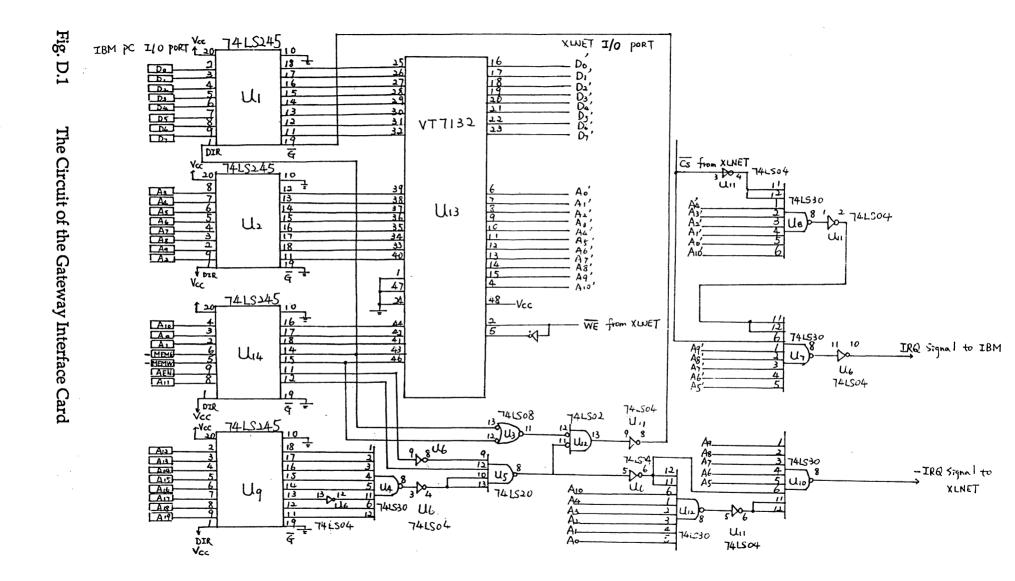

| 5.3                                             | Hardware of the Gateway                      | 78 |  |  |  |

| 5.4                                             | Software Aspects of the Gateway              | 84 |  |  |  |

|                                                 |                                              |    |  |  |  |

|            | 5.4.1 Addressing                               | 85   |  |  |  |

|------------|------------------------------------------------|------|--|--|--|

|            | 5.4.2 Routing                                  | 91   |  |  |  |

|            | 5.4.3 Frame Reformation and Mapping            | 95   |  |  |  |

|            | 5.4.4 The Protocol Translation                 | 98   |  |  |  |

| Chapter 6. | Performance Analysis                           |      |  |  |  |

| 6.1        | Introduction                                   | 102  |  |  |  |

| 6.2        | Description of the Model                       |      |  |  |  |

| 6.3        | Performance Evaluation                         | 105  |  |  |  |

|            | 6.3.1 Response Time                            | 105  |  |  |  |

|            | 6.3.1.1 The Delay in the Queue in a Half-gate  | way  |  |  |  |

|            |                                                | 106  |  |  |  |

|            | 6.3.1.2 The Delay in the Protocol Conversion   | 109  |  |  |  |

|            | 6.3.1.3 The Delay in the User Data Transfer    | 111  |  |  |  |

|            | 6.3.2 Throughput                               | 111  |  |  |  |

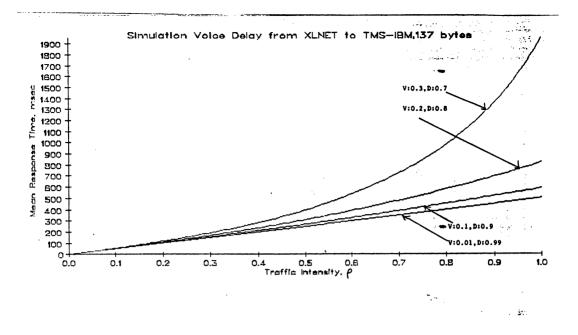

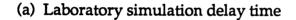

| 6.4        | Simulation Results                             | 113  |  |  |  |

|            | 6.4.1 Packet Arrival Rate                      | 113  |  |  |  |

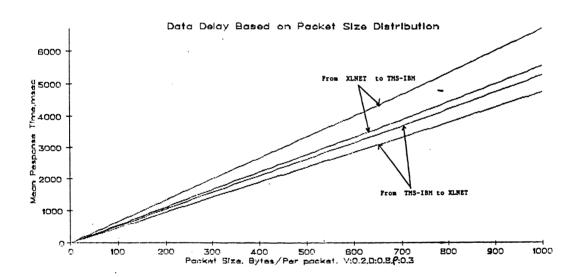

|            | 6.4.2 Packet Size Distribution                 | 125  |  |  |  |

| Chapter 7. | Limitation of the Present Design and Suggested |      |  |  |  |

|            | Improvements                                   | 127  |  |  |  |

| 7.1        | Introduction                                   | 127  |  |  |  |

| 7.2        | Hardware Aspect                                | 127  |  |  |  |

| 7.3        | Software Aspect                                | .127 |  |  |  |

| Chapter 8. | Conclusions                                    | 128  |  |  |  |

# APPENDICES

| А. | TMS380 Adapter Chipset                                    | 131 |  |  |

|----|-----------------------------------------------------------|-----|--|--|

| В. | The Dissimilarity between XLNET and TMS-IBM Ring in the I |     |  |  |

|    | Protocols                                                 | 139 |  |  |

| C. | The Data Sheet of the VLSI VT7132A Dual-port RAM          | 149 |  |  |

| D. | The Gateway Interface Card                                | 161 |  |  |

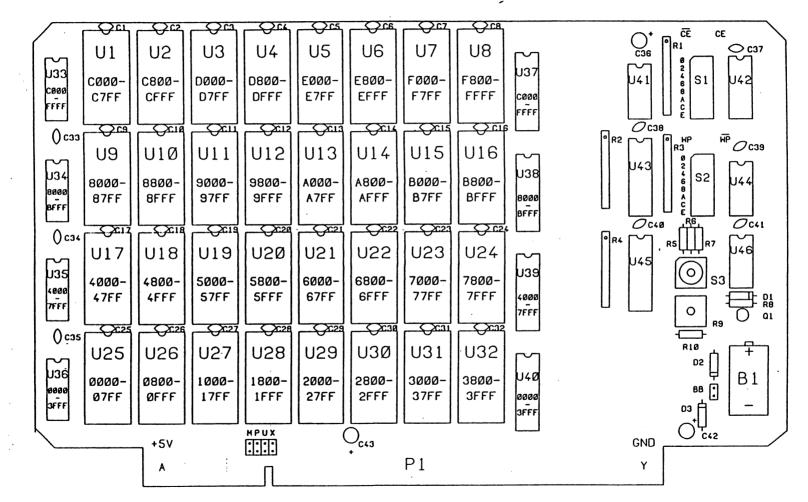

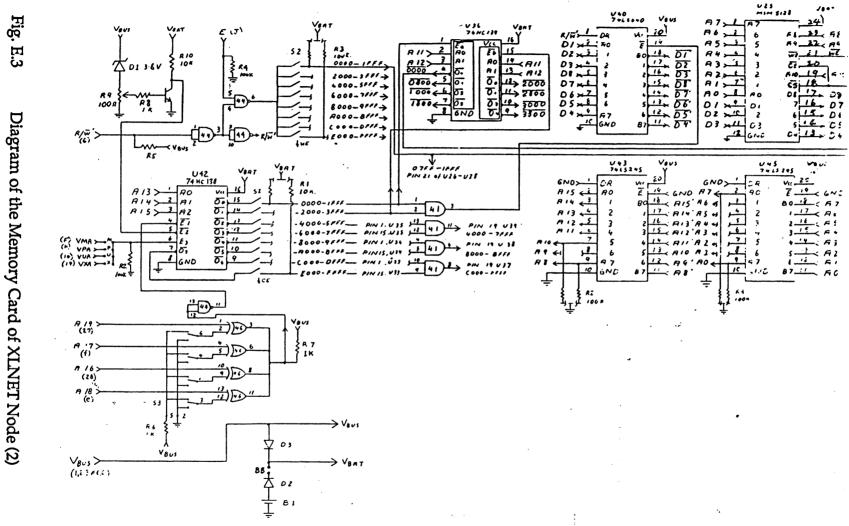

| Е. | Information of the Memory System                          | 165 |  |  |

| F. | Software Program of the Gateway                           | 169 |  |  |

|    |                                                           |     |  |  |

### REFERENCES

# CHAPTER ONE INTRODUCTION

#### 1.1 The Need for a Gateway

Over the past few years, there has been an increasing interest in the design and construction of local area networks (LANs). Some networks are incredibly fast and other are comparatively slow; some provide powerful functions in some fields, and some do not provide them at all. With the increasing use of LANs, the requirement for LAN interconnection arises to overcome limitations in distance, and capability of supporting a huge number of hosts. Hence the need for LANs interconnection.

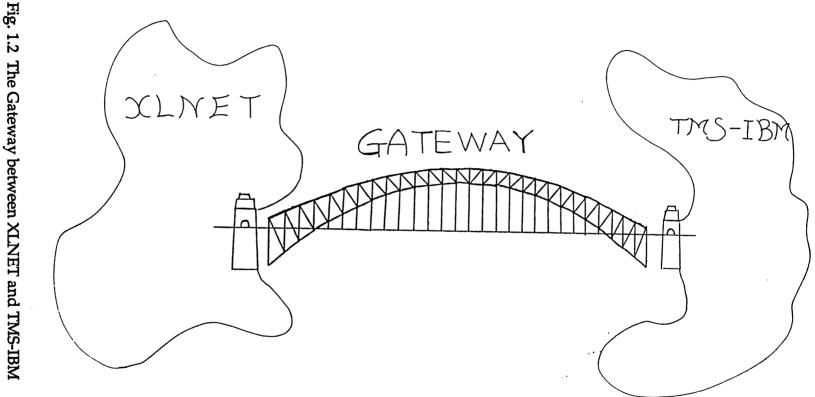

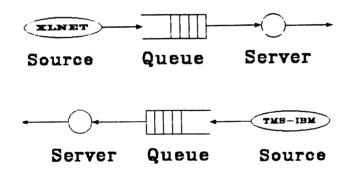

An analogue of interconnecting device is offered the Harbour Bridge in Sydney shown in Fig.1.1. The type of a proper linking device depends very much on the protocol system of each LAN considered. A gateway is a communications link between two dissimilar networks (here XLNET and TMS-IBM Ring). Among others, a gateway translates protocols of source LAN to that of the destination LAN. This thesis is concerned with details of protocol translation, as well as addressing and routing of the messages between two laboratory LANs: XLNET and TMS-IBM Token Ring. The basic model necessitates buffer *ing* of messages for the two direction of the system. (Fig.1.2). The architecture, operating principles and performance of the gateway also presented.

áre

the The Sydney Harbour Bridge is used here as an example illustrating metroppolitan area with the south. gateway function of linking the north part of the Sydney

Fig. 1.1 The Symbol of a Gateway

Cunard's 'Soga Flord' passing beneath Sydney Harbour Bridge.

N

ω

In that follows, we discuss, briefly, the various necessary functions in a gateway by reference to the Open Systems Interconnection (OSI) model.

(1)

### 1.2 The OSI Model

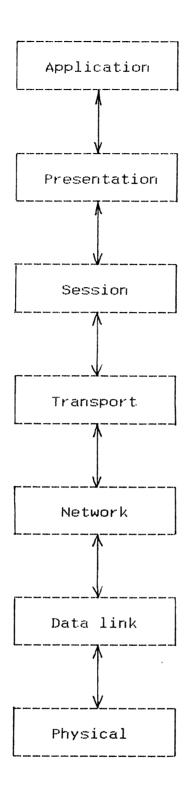

The OSI Reference Model, developed jointly by the International Organization for Standardization (ISO) and the International Telegraph and Telephone Consultative Committee (CCITT), specifies the architecture for open communications. It also assigns functionality to each layer, and identifies how they interrelate. The model consists of seven layers as shown in Fig.1.3.

These seven layers begin at the Application layer, where end users interact with a system or where application software is executed. The user information is eventually passed to the Physical Layer, where logical information is converted into signals that are transported through physical media.

Actually, in the reference model, each layer in the system is contained in a subsystem. Each subsystem contains entities that provide services for a subsystem of higher rank in the model. The network supports entities in a subsystem which together form a layer. Peer-topeer communications between the entities in a given layer are done in accordance with specific rules defined by ISO as protocols. Entities in one layer communicate with entities in another layer through well defined service access points using specific interface protocols.

Fig. 1.3 The OSI layered network model

A brief description of each layer is given below:

1. Physical layer: the physical layer, the lowest layer in the model provides for transmitting raw bits across a communication channel. The responsibilities of this layer are for activating, maintaining and deactivating the physical path. The simplest example is the RS-232-C standard.

2. Data link layer: the data link layer is responsible for error free transfer of data between the nodes and network. It provides for the creation and recognization of frames, their detection and possible correction on account of transmission error. A well known example of a standard for this layer is the High Level Data Link Control (HDLC) protocol.

3. Network layer: the network layer handles the routing functions for data transferred between two open systems. It ensures that packets are correctly received at their destinations and in the proper order. The layer is the highest OSI level supported by some communication networks. The best known standard for this layer is CCITT X.25 providing a packet switched network interface.

4. Transport layer: the transport layer provides the interface between the data communications network and upper three layers. It is responsible for establishing and maintaining transport connections between session entities. The transport layer standards have been developed to provide reliable data transfer, flow control required on an individual basis. The I/SO standard ISO8073 specifies the transport protocol designed to perform these functions.

5. Session layer: the session layer provides the functionality to establish and manage a dialogue between communicating end systems. It is dependent upon the transport layer in the sense that each session connection is handled by one and only one transport connection. The ISO standard ISO8327 specifies the basic session protocol and related options.

6. Presentation layer: the presentation layer provides for the syntax of data in the model, that is, the representation of data. It is to accept data types (character, integer) from the application layer and then negotiate with its peer layer as to the syntax representation. The ISO standard ISO 8823 specifies the basic protocol.

7. Application layer: the application layer is concerned with support of an end user application process. Unlike the presentation layer, this layer provides for the semantics of data. The layer provides service to the users of OSI, not to a next high layer. This layer is seen as containing various protocol, aimed at supporting different type of applications. The best well-known examples are ISO standard IS 8571 File Transfer, Access and Management (FTAM), and IS 8832 Job Transfer and Manipulation Protocol (basic).

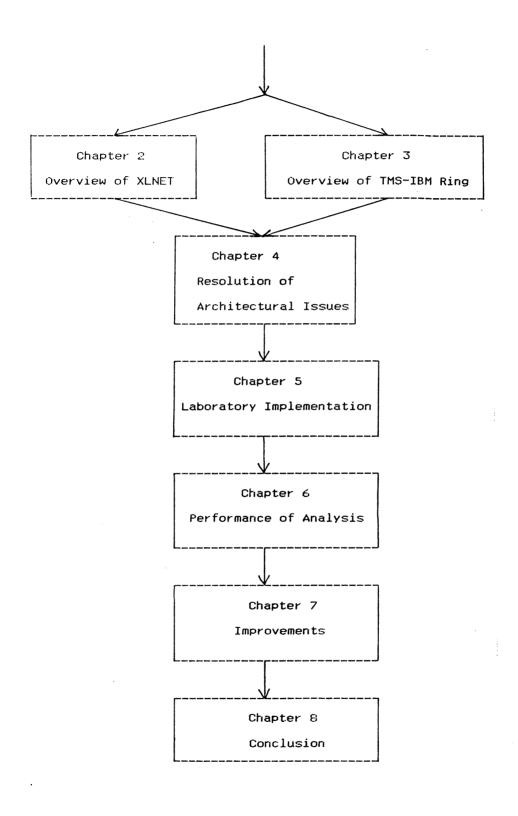

#### **1.3** <u>Structure of the Thesis</u>

The first step in this project is to understand the architecture of the two networks to be interconnected, XLNET and TMS-IBM Ring. Chapters 2 and 3 describe some of the important aspects of the two rings, respectively. After the literature overview, Chapter 4 describes the proposed gateway architecture. A description of the "protocol translator" is also given in this chapter. Chapter 5 describes the laboratory implementation of the internetworking system. In this chapter, the hardware aspects of the gateway and the relevant software will presented.

The performance of the gateway implemented in the internetworking system is analyzed in Chapter 6. In Chapter 7, the shortcomings and possible improvements of this project are discussed. Finally, Chapter 8 summarizes the conclusions. The basic structure of this thesis is outlined in Fig.1.4.

Fig. 1.4 The Structure of this Thesis.

# CHAPTER TWO OVERVIEW OF XLNET

#### 2.1 Introduction

XLNET is a novel local area network with fully distributed architecture, which was originally developed by A.E. Karbowiak and G.J. Anido in the University of New South Wales. XLNET is a LAN based on the Open System Interconnection (OSI) Reference Model to integrate the transmission of voice and data communications. Since, the integration occurs at all levels of the architecture and packet switching is used as the vehicle for integration, XLNET allows the system capacity to be dynamically shared among the users.

This chapter is intended to describe some important aspects of XLNET. In section 2.2, the hardware aspects of XLNET will be presented. Then the XLNET software structure will be briefly introduced in section 2.3. Finally, the main characteristics of the system will be reviewed in section 2.4.

#### 2.2 Hardware Aspects

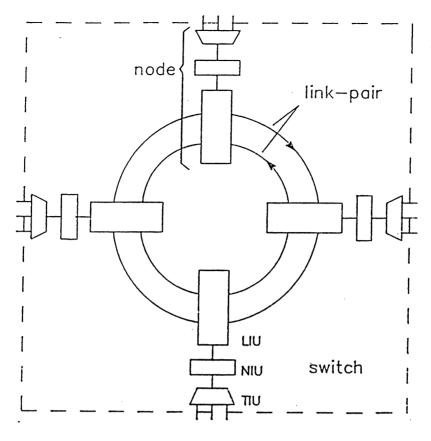

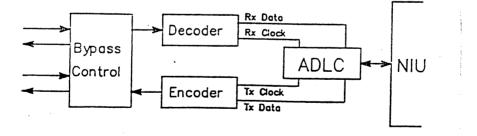

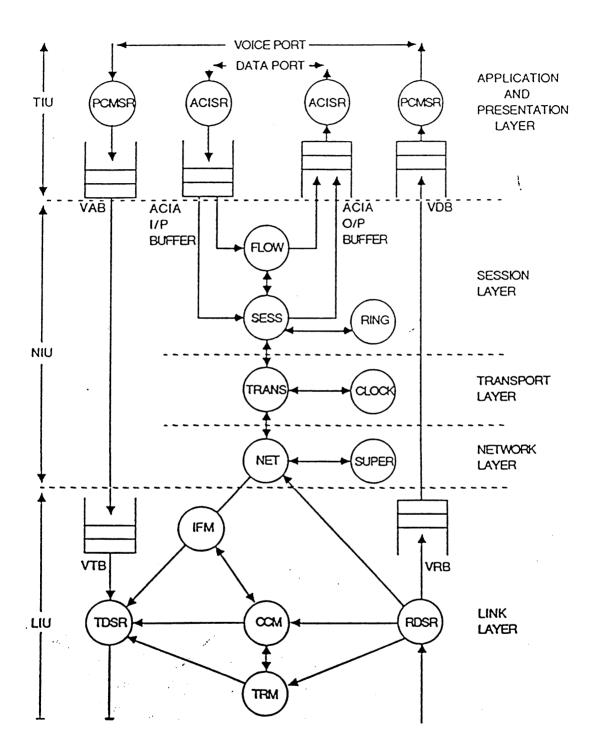

The integrated switching facility of XLNET is shown in Fig. 2.1. The switching entities are called nodes. Each node contains three units. The name and functionalities of each unit are below:

1. Link Interface Unit (LIU): LIU provides interfacing between the node and XLNET ring, enabling logical and physical access to the network. The architecture of the LIU is shown in Fig. 2.2. Details of operating these functions are given in [18].

Fig. 2.1 Switch Architecture

Fig. 2.2 LIU Architecture

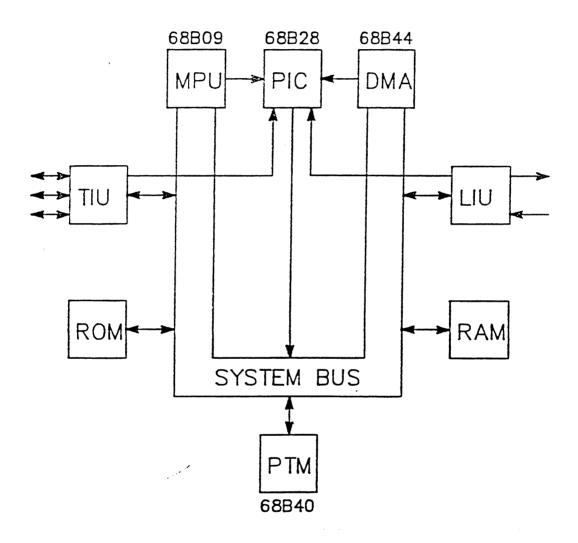

2. Network Interface Unit (NIU): NIU provides the protocol handling capabilities and data processing of the XLNET node. The architecture of NIU is shown in Fig. 2.3. Details of operating these functions are given in [18].

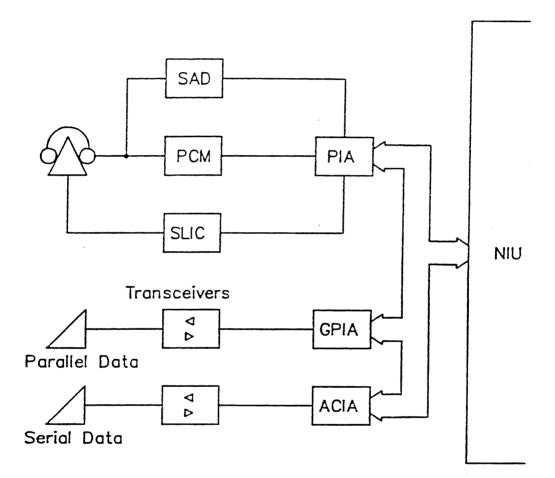

3. Terminal Interface Unit (TIU): TIU provides the physical ports through which the user communicates with the node and with other users on the XLNET. The architecture of TIU is shown in Fig. 2.4. Details of operating these functions are given in [18].

The system prototype specifications are listed in table 2.1 [2].

#### 2.3 Software Aspects

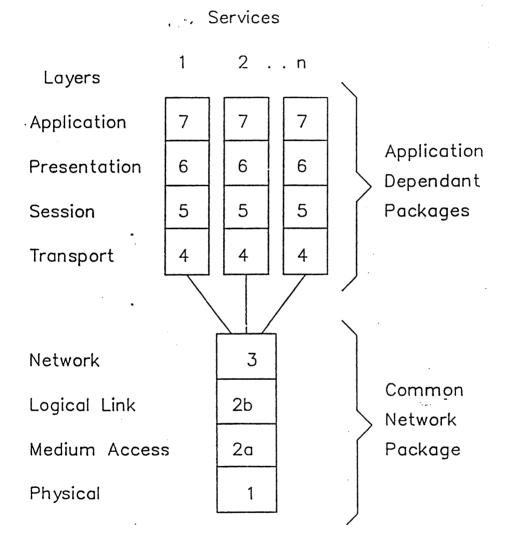

The architecture of network software protocol is based directly on the OSI seven-layered Reference Model. The architecture has the structure shown in Fig. 2.5. The Data Link Layer (layer 2) is further divided into Logical Link Control and Medium Access Control Sub-layers as recommended in the IEEE 802 documents. The Medium Access Control Sub-layer uses many of the recommendations of 802.4 [3, 4], while the 802.2 Class 1 protocol (connection-less operation) [5, 6] is adopted for the Logical Link Control Sub-layer. Further, the OSI Connection-less Network protocol [7, 8] is selected for the Network Layer. The resulting network service offers an efficient and reliable datagram service. For those applications requiring a connection-oriented service, the appropriate choice of Transport Layer software is the OSI Connection-oriented Transport Protocol Class 4 [9, 10] which supports the necessary sequence and flow control.

Fig. 2.3 NIU Architecture

,

Fig. 2.4 TIU Architecture

Fig. 2.5 Protocol Architecture

| Twisted Pair                        |  |  |  |  |

|-------------------------------------|--|--|--|--|

| Biphase-S                           |  |  |  |  |

| 2 M Baud                            |  |  |  |  |

| 255 nodes                           |  |  |  |  |

|                                     |  |  |  |  |

| 1 M bit/second                      |  |  |  |  |

| 3.5 ms (1 K bit packets)            |  |  |  |  |

| IEEE-488; v.24                      |  |  |  |  |

|                                     |  |  |  |  |

| 12 simultaneous calls               |  |  |  |  |

| < 1%                                |  |  |  |  |

| 8 ms (to PSTN)                      |  |  |  |  |

| < 0.4 ms                            |  |  |  |  |

| 150 - 250 ms                        |  |  |  |  |

| Table 2.1: Prototype specifications |  |  |  |  |

|                                     |  |  |  |  |

In essence, the software used in XLNET is composed of a number of routines called processes. These processes are divided into two distinct groups: low-level processes, and higher-level processes.

The low-level processes provide the functions that require critical responses. The functions performed by these processes are associated with the user ports of the TIU such as the handling of voice communications and the functionalities of LIU such as frame reception and transmission. In general, the low-level processes are invoked by the use of hardware and software interrupts.

The higher-level processes perform functions associated with node and network management, and with user-oriented communications. These processes are driven by the operating system XLNCE.

The correspondence between the hardware units, software processes, and protocol layers is shown by the process flow chart in Fig. 2.6. The executive, called XLNCE, provides inter-process communication capabilities for use between the NIU processes by using massage-passing, and between NIU and low-level processes by using mail-boxes. Details of the executive are given in [19].

#### 2.4 Other Significant Features

As previously mentioned, XLNET, is able to integrate the transmission and switching of synchronous and non-synchronous communications (for instance, voice and data). Several advanced schemes, such as efficient integration of data and voice communications within a limited geographical local area, have been employed to provide improved communication capabilities.

The key characteristics of the system are as below:

- Using the distributed cyclic service protocol to transmit voice packet with high efficiency and acceptable delay;

- (2) Using speech interpolation to increase voice carrying capacity.

- (3) Using variable time-slot to improve data carrying efficiency.

- (4) Using a decentralised architecture to enhance reliability.

In the following sub-sections, these functions will be examined in detail and some special features of XLNET will be discussed as well.

Fig. 2.6 Process Flow Graph showing the main Interrup and XLNCE processes and the main interprocess communication paths

#### 2.4.1 Strategy of Token Generation

The medium access mechanism of XLNET is based on the token ring passing protocol IEEE 802.4 [3]. In a ring topology, network nodes are linked by a form of closed ring. Message or information, in the form of frames or packets (the frame format of XLNET shown Fig. 2.7), normally flows unidirectionally around the ring. In the token passing mechanism, a token is a unique symbol representing the right to access the network. The token format of XLNET is shown in Fig. 2.8. Initially, a free token generated by a designated node (monitor) travels around the ring until a node ready to transmit converts it into the opening flag of the frame. The node proceeds to transmit the remainder of the frame, following which the token is released.

The strategy employed for token generation plays an important role in the token ring passing protocol. There are three possible strategies:

(1) Single packet mode: the transmitting node has to wait until the frame completely circulates the ring before releasing the token into the ring.

(2) Single token mode: its operation is different from the first in that, the transmitting node need only wait until the head of the frame rotates around the ring.

(3) Multiple token mode: the token is released at the end of the frame transmission.

| FLAG | DA | SA | FC | INFORMATION | CRC | FLAG |

|------|----|----|----|-------------|-----|------|

|------|----|----|----|-------------|-----|------|

FLAG = 01111110 (1 OCTET)

DA = DESTINATION ADDRESS (1 OCTET)

SA = SOURCE ADDRESS (1 OCTET)

FC = FRAME CONTROL (1 OCTET)

•

INFORMATION = INFORMATION FIELD (n OCTETS)

CRC = CYCLIC REDUNDANCY CODED CHECK SEQUENCE (2 OCTETS)

Fig. 2.7 Frame format

TOKE

TOKEN = 0.1111111 (1 OCTET)

(b) Token Format

Fig. 2.8 XLNET token

In the consideration of frame service time, a choice of suitable strategy employed in the token ring depends on the nature of the ring. On small rings with a roundtrip delay smaller than the frame transmission time, under the operation of single token mode, the service time is simply equal to the transmission time; otherwise, it is equal to the roundtrip delay. In contrast, on large rings with a roundtrip delay larger than the frame transmission time, the multiple token mode is a better choice than other modes since the service time always equals the transmission time.

In our interconnected network system, the multiple token mode is employed in XLNET, while the single token mode is used in TMS-IBM Ring (see Chapter 3).

#### 2.4.2 Distributed Cycle Service Scheme

In this sub-section, the distributed nature of the cyclic service scheme will be considered.

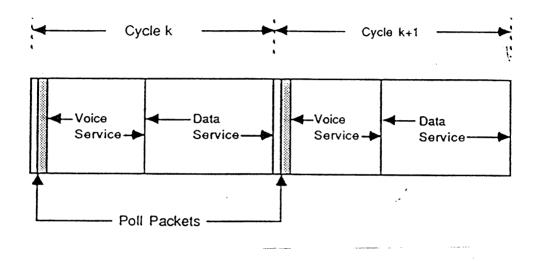

In common with other members of the cyclic service networks such as the Zurich Ring [11, 12] and Welnet [13], XLNET operates by dividing the time scale into fixed length intervals called cycles shown in Fig. 2.9. The first part of each cycle, called voice service sub-cycle, is given to voice traffic, while the remainder of the cycle, called data service sub-cycle, is offered to data traffic. The cycle duration is chosen to equal the voice packet generation time, 16 milliseconds.

XLNET employs a control packet, called the poll packet (whose format shown in Fig. 2.10), corresponding to a timestamped packet [14] as the basis for a voice synchronisation mechanism. The poll packet is generated at the start of a given cycle by the controller of that cycle. The controller, called the polling node, maintains a cycle timer.

Fig. 2.9 Cycle Structure showing voice service, which starts following the transmission of the Poll packet, followed by data service.

| HEAD | DA | SA | CONTROL | TIMESTAMP | TẠIL |  |

|------|----|----|---------|-----------|------|--|

|      |    |    |         |           |      |  |

Fig. 2.10 Poll packet format showing the Timestamp field which, upon reception, contains the time since the current cycle started.

(DA: Destination Address, SA: Source Address)

As a result of the poll packets, the cycle timers of all nodes are synchronised. When the end of each cycle is reached, the cycle timer in each node will timeout, and the first node to receive the token following the end of each cycle creates and issues a poll packet, the first token arrival at each node following the poll packet is used for voice service, with subsequent arrivals for data service.

If the number of voice packets requiring service during any given cycle exceeds the capacity of the system, then the token will not make it back to the polling node prior to the end of the cycle. Rather than the fixed location of the cyclic service controller, the location of that in XLNET is distributed. In other words, it is not bound to any particular location on the ring, but in response to the applied load. A number of advantages are achieved by using such a distributed controller:

(1) The performance penalties [14] by the use of a centralised control of service cycle are eliminated. Since the location of the controller will vary from cycle to cycle, no node will be favourably served during any service cycle. In other words, the desire of the fair access to the ring medium is reached.

(2) The voice synchronisation technique can be applied. Since the cyclic service controller periodically issues a timestamped packet which is always generated at the start of a cycle, it is able to meet the requirement to reach the voice synchronisation. Sub-section 2.4.3 will discuss it in greater detail.

(3) Reliability is promoted since control of the cyclic service and voice synchronisation is not based on any particular node.

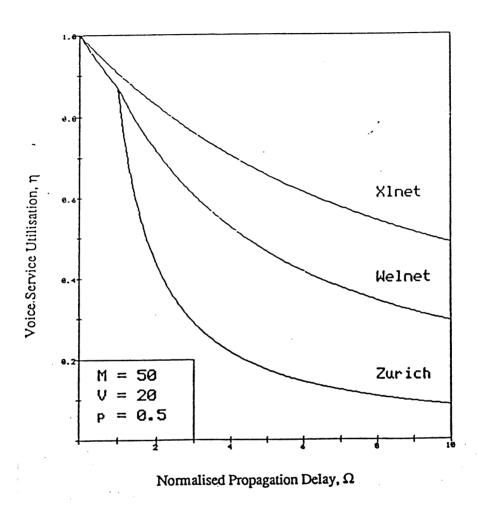

The performance, associated with probability of packet discard and loss of voice capacity by means of the distributed cycle service scheme, was analyzed by Gary Anido [14]. The comparison of voice service utilisation for XLNET, Zurich Ring and Welnet is shown in Fig. 2.11. The latter two networks employ centralised cycle service controllers.

#### 2.4.3 Efficient Improvement On Voice Service

In general, there are two problems encountered in networks which employ packet switching for voice. First, the excessive voice delay causes echo problems on PSTN calls. Secondly, the delay variance results in glitching in the receive voice signal.

XLNET has successfully solved this problem by the use of a "Cyclic Service Switching Scheme", discussed in section 2.4.2, for the integration of voice and data. The scheme allows the echo delay on calls to the PSTN to be arbitrarily small. Furthermore, the scheme can be applied for an elegant variance smoothing technique to overcome the glitching the receiving signal.

How can the cycle service scheme be a powerful weapon for shooting the two troubles above? The explanations will be presented in the following paragraphs.

In XLNET, all the nodes in the ring are synchronised at the beginning of a cycle by a polling frame, the voice packets assembled in the previous cycle are serviced in the current cycle. When the voice packets arrive at the destination node, they will not be played out until the beginning of the next cycle. Hence a voice delay is the constant end-to-end delay which is equal to two cycle durations.

Fig. 2.11 Comparison of voice service utilisation for the three systems (Zurich ring, Welnet, and XLNET).

The end-to-end delay for a voice packet is defined as the sum of the packetisation delay and the transfer time, that is

$\mathbf{D} = \mathbf{T} + \mathbf{T}\mathbf{f}$

where D is the end-to-end delay, T is the cycle duration (equal to the packetisation delay), and Tf is the transfer time which is defined as the time from when a packet is assembled to the time it is disassembled at the destination node.

If the transfer time is allowed to vary, the end-to-end delay also varies. It results in discontinuous voice output forward to the receiver, called "glitching" [15]. The implementation of Minoli's "Receive End Buffering" with "Limited Waiting for Late Packet" [16] employed one method to overcome this problem. This method succeeds by inserting a delay 'Dy' to smooth the delay variance. This introduced delay is employed to augment the transmission delay "Dt' such that the transfer delay is a constant. the formula is below:

Tf = Dy + Dt = T [seconds]

The introduced delay Dy is bound by T (equal to one cycle time).

In XLNET, by means of the evolutionary cycle service scheme, the end-to-end delay is a constant equal to twice the cycle duration. The voice signal reproduced by the destination node is essentially continuous. Therefore, the problem of "glitching" is solved.

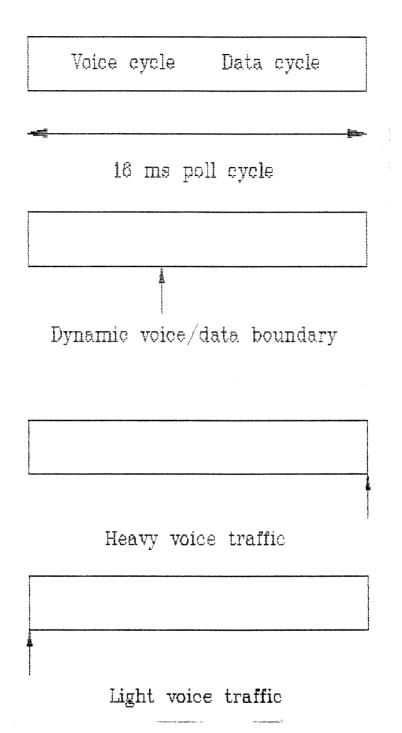

## 2.4.4 Speech Interpolation and Its Advantage

Since XLNET uses the fair access and distributed cyclic service scheme, there are no pre-assigned locations within the voice service for specific voice sources. Under this circumstance, the use of speech interpolation is readily accommodated. If a voice user is currently silent, then no packet is transmitted during the voice cycle. In this case a token is passed without serving a packet when it arrives at the node during the voice service, the duration of the voice service is reduced and effective data capacity is increased. When the user returns to talkspurt and is generating voice packets, the increased voice service is accommodated by borrowing back the capacity previously made available to data. The flexibility is contributed by the "Dynamic Boundary" shown in Fig. 2.12 [16] in the cycle service scheme.

By means of this technique, under heavy voice traffic, much of the nominal capacity will be used for most of time. Furthermore, under light voice load, data sources are able to use nearly the entire system capacity. In a word, the speech interpolation, together with the dynamic boundary is a key scheme used to improve the utilisation of the system capacity.

Fig. 2.12 Dynamic voice/data boundary in XLNET

#### CHAPTER THREE

#### **OVERVIEW OF TMS-IBM TOKEN RING**

#### 3.1 Introduction

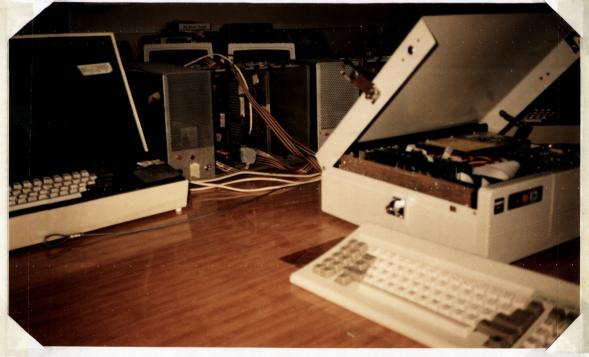

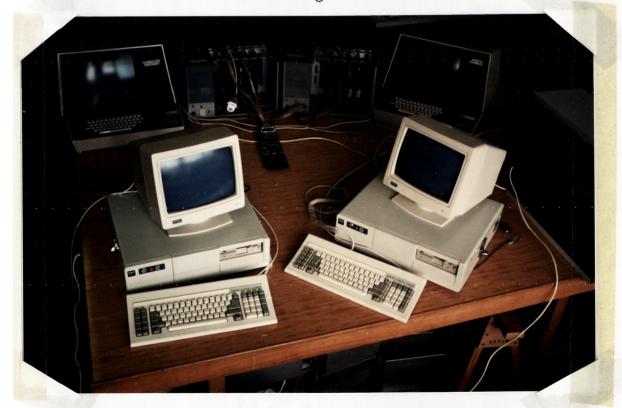

The TMS-IBM Token Ring, based on the token ring architecture with a star wired configuration, is designed to carry computer traffic. It uses the TMS-380 chipset [20]. The integration of voice and data in the IBM ring was successfully achieved by T.L. Ng at the University of New South Wales in 1987 [21]. The operating system of TMS-IBM Ring, NET-OS is not a feature of the TMS commercial product, but is designed by T.L. Ng to be used into the network system with the TMS-380 adapter chipset and IBM XT/PC machine. The gateway we have realised bridges this implementation of the IBM Ring on one side and XLNET (see Chapter 2) on the other.

In section 3.2, the key architecture of the hardware, TMS-380 adapter chipset will be discussed. The software, NET-OS, and the operation of the TMS-IBM Token Ring will be introduced in section 3.3. Finally, in the last section of this chapter, section 3.4, we present an overview of the main characteristics of the system.

#### 3.2 Hardware Aspects--TMS-380 Adapter Chipset

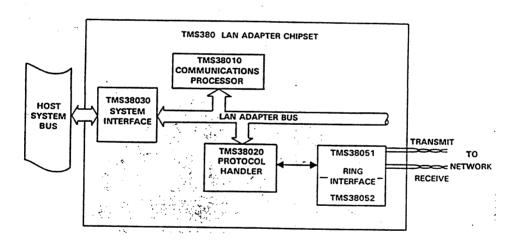

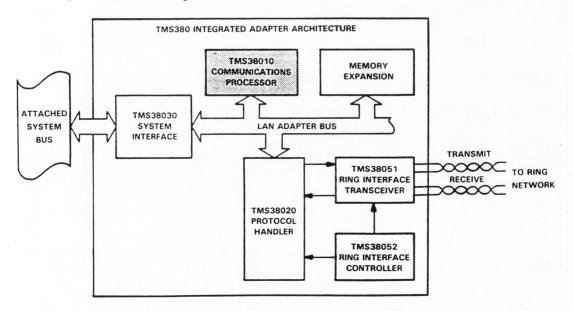

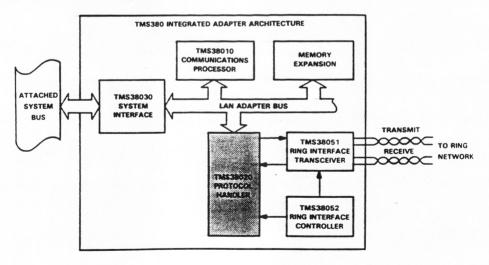

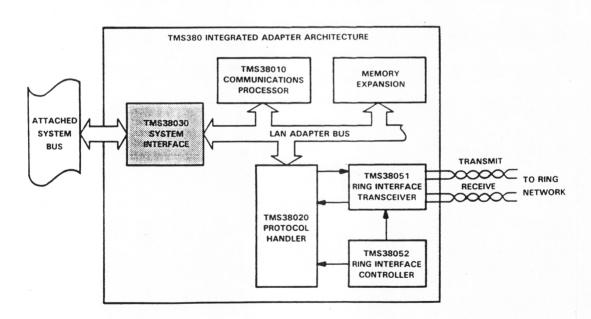

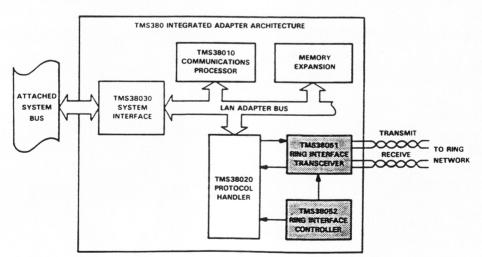

The implementations of the Physical Layer and the Medium Access Control Sub-layer of the TMS-IBM token ring network are realised by the TMS-380 adapter chipset, which was developed by the Texas Instruments and IBM, in the spring of 1985. The main feature of the adapter architecture is shown in Figure 3.1 [20]. The adapter essentially consists of five VLSI chips which together enable a transmission of 4 megabit per second signal through the twisted pair wire.

. . . . . . . . .

Fig. 3.1 TMS380 Integrated Adapter Architecture

Furthermore, as the adapter works as a front-end processor to execute the host-independent operation in the LAN, it does not only reduce the burden of the host system in the LAN, but also provides a reasonable degree of reliability for data transmission.

The function of the main components of the adapter chipset are summarized in the following sub-sections.

#### 3.2.1 TMS38010 Communications Processor (CP)

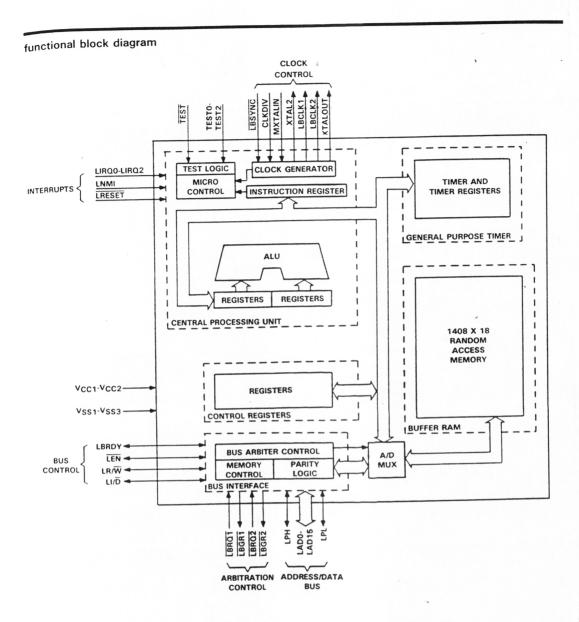

The Communication Processor contains a dedicated 16 bit CPU with 2.75k bytes of on-chip RAM. The CP executes the adapter software resident within the TMS38020 (Protocol Handler). Besides, it maintains on-chip RAM buffers the frame being received and transmitted. The chip provides single cycle arbitration of the 3 MHz LAN adapter bus for maximum data throughput in the adapter chipset. A more detailed functional block diagram is given in the Appendix A.1.

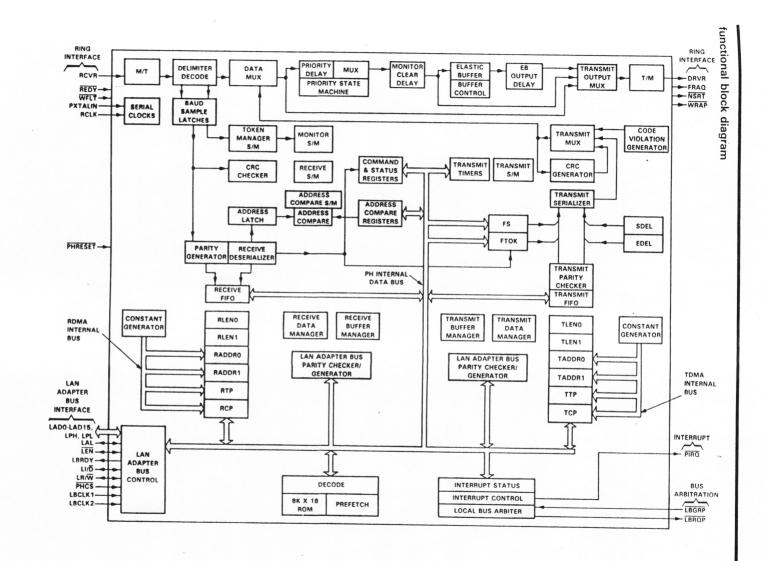

#### 3.2.2 TMS38020 Protocol Handler (PH)

The Protocol Handler performs hardware based protocol functions for a 4-megabit per second token ring LAN compatible with the IEEE 802.5 standard. The adapter software, contained within the 16k byte onchip ROM and executed by the Communications Processor, supports LAN management services, diagnostic coverage and ring operation. The PH implements frame address recognition and Differential Manchester encoding/decoding. To insure high-speed frame transfer between the ring and the adapter's buffer RAM, the PH provides 4 DMA channels, two for receive and two for transmit. The detailed functional block diagram is collected in Appendix A.2.

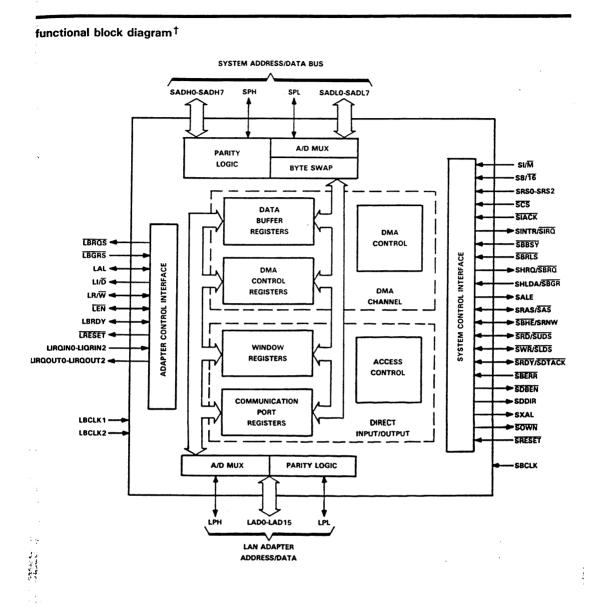

#### 3.2.3 TMS38030 System Interface (SIF)

The System Interface (SIF) offers up to 40 megabits per second of data to the host system via its own built-in DMA transfers. as its name implies, the SIF acts as the interface between the host system and the adapter chipset card through the System Command Block, the System Status Block and the interrup registers. A more detailed functional block diagram is given in Appendix A.3.

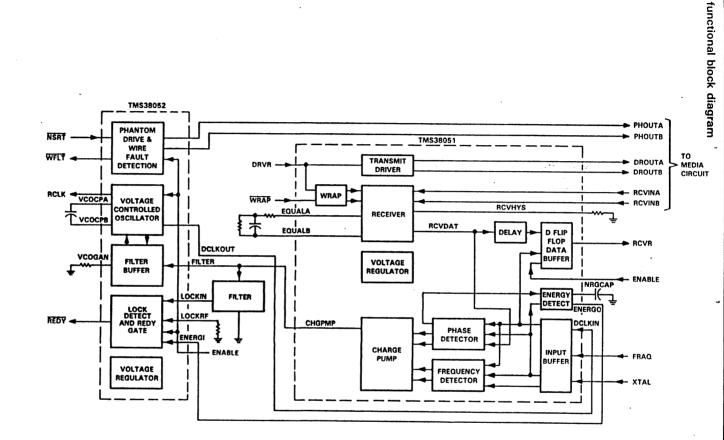

## 3.2.4 TMS38051 Ring Interface Transceiver (RIT) and TMS38052 Ring Interface Controller (RIC)

The Ring Interface Transceiver and Controller provide the functions for the ring interface, such as the clock for the ring when in active monitor mode, a phase locked loop for clock recovery, phase alignment, data detection, error detection of wire faults, a loop-back path for diagnostic testing and so on. The two chips, in conjunction with the above three chips, form a highly integrated token ring LAN adapter compatible with IEEE standard 802.5-1985 Token Access Method and Physical Layer Specifications. A more detailed functional block diagram is given in Appendix A.4.

#### 3.2.5 The Operation of the TMS-380 Adapter

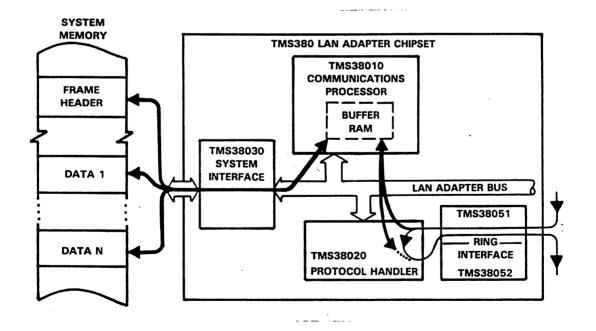

The adapter presents a full duplex interface to the IBM XT-PC host system with separate receive and transmit channel between the adapter and the LAN, and a 48-megabit per second LAN adapter bus with singlecycle arbitration for internal adapter transfer. Furthermore, a 40-megabit per second DMA controller connects the LAN adapter bus to the host system bus. Figure 3.2 [20] shows data flow through the TMS-380 adapter chipset.

In particular, the PC host system and the adapter pass information through a shared memory which contains the System Command Block (SCB) and System Status Block (SSB), to each other. The adapter can be initialized to meet specific host system bus requirements. The initialization parameters include:

- (1) Interrupt routines.

- (2) Buffer sizes.

- (3) Allocation of these buffer to transmit and receive channels.

- (4) Expansion memory.

- (5) The setting of addresses.

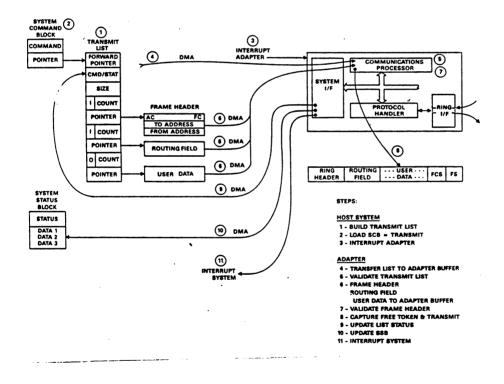

As mentioned earlier, the communication between the adapter and the host system is via the SCB and SSB. A procedure of a typical transmit operation is shown in Figure 3.3 [20]. Before transmitting a frame, the PC host first sets up the SCB which contains the transmit command and the starting address of the transmit list in the host system memory. Then, the host interrupts the adapter. After receiving an interruption from the host, the adapter DMA reads the SCB, and according to the address of the transmitted frame in the SCB, the adapter DMA reads the whole frame to the adapter RAM. Having the validation on the transmit list and frame format, the adapter captures a free token and transmits the frame onto the LAN. The frame will circulate until it returns to the sender adapter, where it is removed from the ring and a free token is released to the LAN. The SSB is then updated by the adapter and sent to the host system via the adapter DMA.

Fig. 3.2 Adapter Data Flow

Fig. 3.3 Transmitting A Frame

In a similar fashion, the host issues a Receive Command via SCB to the adapter pointing to the receive list in host system memory. Upon reception of a frame, the adapter will transfer the receive list from the host system to the adapter RAM via DMA, then transfer the received data to the appropriate location in the host system memory via DMA as well, and finally update the SSB.

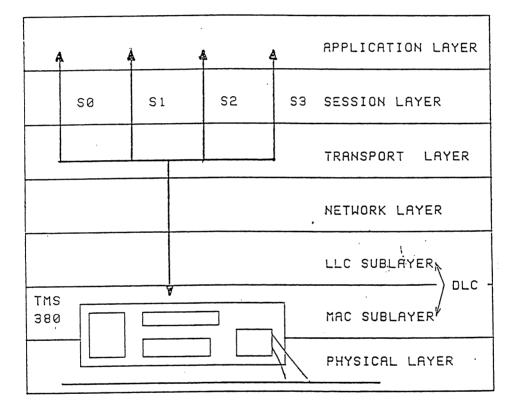

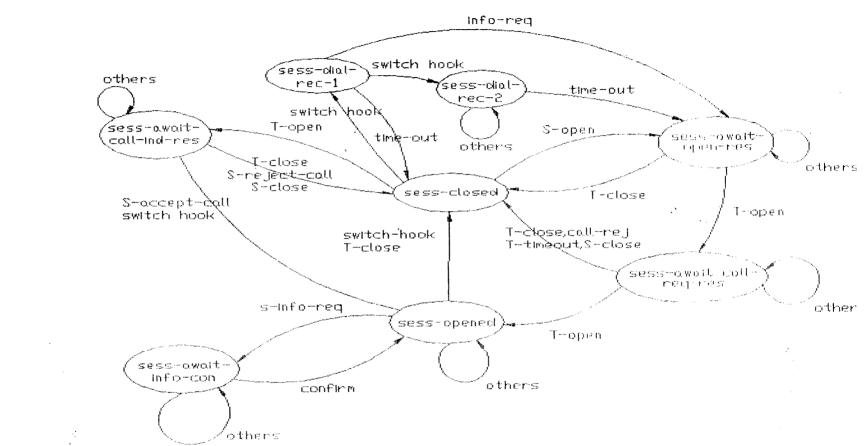

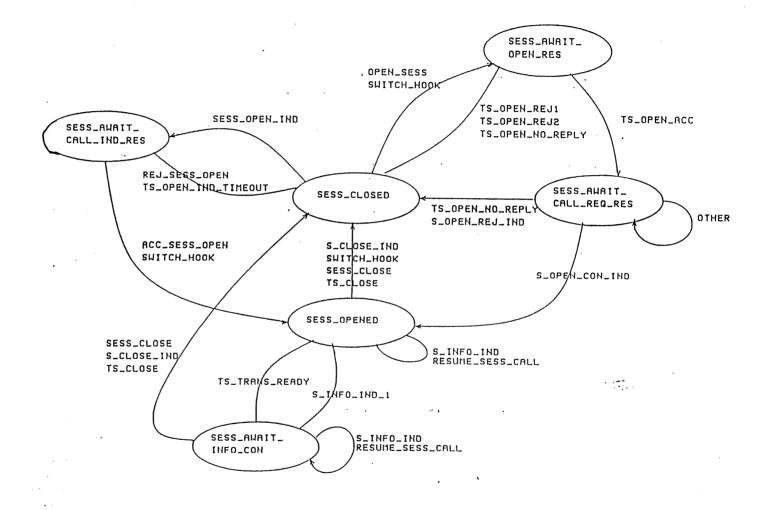

#### 3.3 Description of Software

Taking the advantages of the modularity of design of open systems, the network software architecture, as in XLNET, is based on the OSI seven-layered Reference Model. The architecture has the structure shown in Fig. 3.4. The Physical Layer and Medium Access Control Sub-Layer (IEEE 802.5 Token Passing Ring [22]) are provided by the hardware and firmware in the TMS-380 adapter chipset, which has just been discussed in the last section. The Logical Link Control Layer, Network Layer and Transport Layer employ the protocols similar to those of XLNET, the IEEE 802.2 Class 1 Protocol, the OSI Connection-less Network Protocol and OSI connection- oriented Transport Protocol Class 4, respectively. The protocol of the Session Layer is designed by T.L. Ng [21].

Under this protocol structure, the system does not only offer datagram service to implement the integrated communications (data and voice), but also provides functions such as flow control, error recovery, and the ability to mutiplex multiple transport connections on to one network connection.

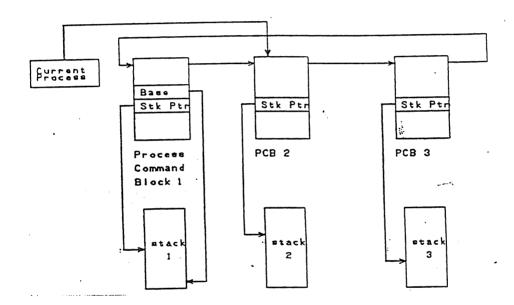

Fig. 3.4 Layered Architecture

As with XLNET, the software used in TMS-IBM Token Ring is composed of several routines, called processes. The processes are divided into two distinct groups: synchronous processes and non-synchronous processes. Indeed, the functions provided by the two kinds of processes are similar to those offered by the low-level processes and the higher-level processes in XLNET as well. The synchronous processes are driven by the operating system NET-OS [21] which takes advantages of the multitasking environment [23] to process tasks concurrently. At the heart of the NET-OS is a table of process Command Blocks. Each process command block contains information pertaining to the status of each process (shown in Figure 3.5 ). Non-synchronous processes, on the other hand, are interrupt driven.

#### 3.4 Special Features

The contribution of NG Lee is to implement an efficient integration of voice and data communications in the TMS-IBM Token ring. Although some of the protocols employed here, as mentioned earlier, are quite similar to those in XLNET, there are several techniques significantly different from those in XLNET. In the following sub-sections, those dissimilar but important schemes will be examined.

#### 3.4.1 The Integration service

The switching scheme for the integrated communications, in TMS-IBM Ring, is based on the nature of multiple level priority packets, in lieu of the distributed cycle service technique in XLNET.

## Fig. 3.5 NET-OS Environment

According to Bux [24], the performance of the integration achieved at the Medium Access Control Sub-layer such as the case of XLNET should be better than that at any other level of the OSI reference model. However, the protocol of the Medium Access Control Sub-layer provided by the firmware of TMS-380 adapter chipset is invisible and inaccessible for commercial reasons. Therefore, the integration is impossible to be implemented in this level, although it can be done at a higher level, namely the Logical Link Control (LLC) Sub-layer. In TMS-IBM Ring, the LLC sub-layer assigns voice packets a higher prority over data packets, and maintains two queues for these two kinds of packets. Whenever a free token arrives at a node requiring service, the voice queue is served first, following that, the data queue is served until the token-holding timer times out [21].

#### 3.4.2 The Scheme of Speech Interpolation

The scheme used to overcome the problem generally associated with voice communications in packet switched network, such as the delay of voice, is Minoli's "receive end buffering" with "limited waiting for late packets". The comparative principle and operation of the scheme for smoothing the voice packets' delay between XLNET and TMS-IBM Token Ring have been presented in section 2.4.3.

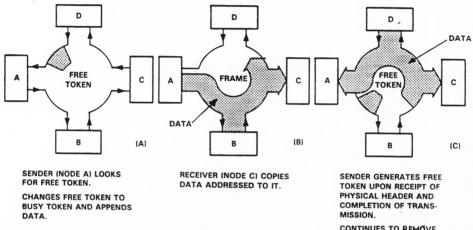

### 3.4.3 Token Access Techology

As mentioned previously, the TMS-IBM Token Ring employs a token passing access method with a star-wired ring topology as described by IEEE 802.5. Figure 3.6 [20] shows the topology of token passing access with 4 nodes A,B,C,D connected in the ring. When there is no data being transmitted, a free token will circulate unidirectionally around the ring.

The token format is show in Figure 3.7 [20] which consists of three bytes: STARTING DELIMITER, ACCESS CONTROL, ENDING DELIMITER. If any of the nodes, such as node A, desires to transmit a frame through the ring to a destination such as node C, the steps it must follow are listed below:

(1) Wait for the free token.

(2) Seize it on its arrival.

(3) Mark it 'busy' by setting a specific bit in the access control field of the token format.

(4) Convert it into a data frame with the format shown in Figure 3.8.[20].

Upon recognising the destination address of the transmitted frame the receiving node C copies the data frame as it passes through the interface. Node A that originated the frame has the responsibility for removing the frame when it circulates back, and releases a free token onto the ring for the other nodes to use. It is worthy to mention that the difference between a token and a data frame is not only as regards their lengths but also the status of the specific bit in the access control field. If the specific bit is set, the token is occupied and becomes part of the header of a data frame; otherwise the token is free. Token passing access provides priority levels to be assigned to tokens, thus providing support for synchronous traffic. As there is always one token on the ring and possession of the token gives that node exclusive use of the ring, for the purpose of fair token access to the ring for all the nodes, a token-holding timer restricts the maximum time a node can use the token before passing the token.

CONTINUES TO REMOVE DATA UNTIL RECEIPT OF PHYSICAL TRAILER.

Fig. 3.6 Token Passing Example

Fig. 3.7 Free Token Format

|  | STARTIN<br>DELIMITE<br>1 BYTE |  | FRAME<br>CONTROL<br>1 BYTE | DESTINATION<br>ADDRESS<br>6 BYTES | SOURCE<br>ADORESS<br>6 BYTES | INFORMATION<br>FIELD | FRAME<br>CHECK<br>SEQUENCE<br>4 BYTES | ENDING<br>DELIMITER<br>1 BYTE | FRAME<br>STATUS<br>1 BYTE |

|--|-------------------------------|--|----------------------------|-----------------------------------|------------------------------|----------------------|---------------------------------------|-------------------------------|---------------------------|

|--|-------------------------------|--|----------------------------|-----------------------------------|------------------------------|----------------------|---------------------------------------|-------------------------------|---------------------------|

......

....

. . . . . . .

.....

Fig. 3.8 Frame Format

#### **CHAPTER FOUR**

#### **RESOLUTION OF ARCHITECTURAL ISSUES**

#### 4.1 Introduction

An appropriate resolution of internetwork architectural issues plays a very important role in the internetwork design. The key to the resolution is dependent on the applications of the internetwork system and the technologies used in its constituent networks. This chapter discusses the solutions of the key architectural issues in the internet work system considered here.

An interconnected set of networks is referred to as an internet, and a constituent network in an internet is referred to as a subnet. In addition, subnets are connected by devices which are referred to as gateways. A gateway provides a communication path to exchange messages between subnets. Under this internetworking architecture, the first issue which is discussed in section 4.2 is the strategy taken to achieve the subnet independence. Secondly, the four possible approaches, "bridge, X.75, Internet protocol and Protocol translator", applied to internetworking will be briefly described in section 4.3. The last one, Protocol translator, was chosen as the approach for the internet. The reasons for this choice are given as well. Section 4.4 discusses the connection-oriented and connectionless communication services. The next issue to be discussed in section 4.5 is the addressing methodology. Then, the shortcomings of the implementation on the segmentation and reassembly in the considered internet will be given in section 4.6. Finally, section 4.7 explains why routing is not necessary in the particular implementation.

### 4.2 <u>Subnet Independence</u>

There is a large investment in the hardware and software of the two existing networks, XLNET and TMS-IBM Token Ring. As far as possible, the internet protocols should be transparent to the two existing subnets. Obviously, some changes to the software of the two systems need to be made, but we shall follow the principle: the fewer changes, the better.

Two possible strategies are considered:

(1) Internet messages are embedded in the subnet messages as user information (see Fig.4.1.), just as Network layer messages are embedded in the Data Link layer messages. The internet header contains the destination subnet and station addresses. The subnet header contains the address of the next gateway. The gateway removes the first subnet header and trailer and adds new ones before transmitting the message to the next gateway and so on. The internet message is thus completely transparent to the local network, but this scheme has the shortcoming of increased overhead of the local as well as internet headers and trailers. Furthermore, as the technique is designed for mutiple-gateway internetworking systems, it is not employed in our one-gateway two-subnet internetworking system.

| Subnet | Internet |           | Internet | Subnet  |

|--------|----------|-----------|----------|---------|

| header | header   | User Data | trailer  | trailer |

# Fig. 4.1 Imbedded Internet Messages

| Internet/subnet |           | Internet/subnet |

|-----------------|-----------|-----------------|

| header          | User Data | trailer         |

# Fig. 4.2 Compatible inter/subnet Network layer

(2) If the Network layer of the subnet is designed with internetworking in mind, then the network header can be considered as the internet header. This is achieved by adding additional fields to existing protocols and formats (see Fig.4.2). This minimizes changes but allows internet and local message to be differentiated. Each subnet is able to interpret an internet address and route the internet message to an appropriate gateway. This method is employed in the implementation of the internet communications. The Network layer of each subnet is modified into internetworking functionalities by adding the source and destination network addresses to the existing formats.

## 4.3 Internetwork Architectures

The solution to the interconnection of different types of LANs is by the use of appropriate gateways and bridges. The type of gateway or bridge used varies depending on the extent of homogeneity between the constituent networks at the various layer protocols.

To assist in choosing an appropriate approach for implementing the internetworking functions, the similarities and differences between XLNET and TMS-IBM Token Ring at their respective OSI layers are listed in Table 4.1.

| OSI layer            | XLNET                                 | TMS-IBM Token Ring  |  |

|----------------------|---------------------------------------|---------------------|--|

| Application          | Undefined                             | Undefined           |  |

| Presentation         | Undefined                             | Undefined           |  |

| * Session            | Designed                              | Designed            |  |

|                      | by Gary Anido                         | by T.L. Ng          |  |

| * Transport          | OSI Connection-<br>oriented Transport | Similar to<br>XLNET |  |

|                      | protocol Class 4                      |                     |  |

| Network              | OSI Connection-                       | Same as XLNET       |  |

|                      | less Network<br>protocol              |                     |  |

| Logical Link Control | IEEE 802.2 Class 1                    | Same as XLNET       |  |

| (LLC)                | Connection-less                       |                     |  |

|                      | operation                             |                     |  |

| * Medium Access      | IEEE 802.4                            | IEEE 802.5          |  |

| Control (MAC)        | Token Bus                             | Token Ring          |  |

| * Physical           |                                       |                     |  |

| 1. Bit level         | Mutual method                         | Master clock        |  |

| synchronisation      |                                       | method              |  |

| 2. Line code            | Biphase-S code  | Differential    |  |

|-------------------------|-----------------|-----------------|--|

|                         |                 | Manchester code |  |

| 3. Transmission         | Ribbon cable or | Twisted pair or |  |

| medium                  | optical fibre   | optical fibre   |  |

| 4. Electrical Interface | RS-422 standard | TMS 38051 &     |  |

|                         |                 | 38052           |  |

Table 4.1 The OSI layer protocol comparison between XLNET and TMS-IBM Ring

\* The operating system of XLNET is written in 6809 assembly language and runs in the 6809 microprocessor and related chips (see in Chapter 2).

\* The operating system of TMS-IBM Token Ring is written in Turbo Pascal Ver.3 and runs in the IBM XT/PC. (see in Chapter 3)

\* The two systems use their own version of Session layer protocol. The comparison between them is made in Appendix B.1.

\* Even though OSI Connection-oriented Transport protocol class 4 is selected for the Transport layers of both networks, some differences existing in the protocols between the two networks in this layer are explained in Appendix B.2.

\* The MAC and Physical layers of TMS-IBM Token Ring are provided by the TMS-380 adapter chipset.

\* More detailed information about the Physical layer in the two networks can be found in [25] and [20].

Of the possible approaches for internet gateway design, four are commonly encountered in the internet communication systems: bridge, X.75, IP and protocol translator. Whether the above four approaches can be satisfied with the requirements of the proposed internet will be examined in the following sub-sections.

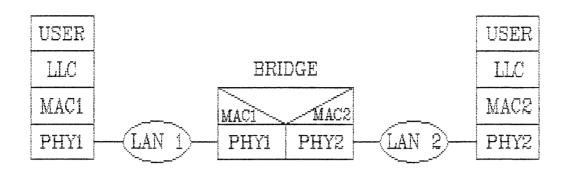

#### 4.3.1 Bridge

A bridge [26,27,28] is a simplified gateway: it can be used to connect homogeneous networks. It operates within the Data Link layer, and higher Network layers are not involved. For LANs, the Data Link layer is further subdivided into the Logical Link Control (LLC) sub-layer and the Medium Access Control (MAC) sub-layer. Bridges are referred to as MAC layer bridges. As shown in Fig. 4.3, whenever user data is provided to LLC by an LLC user (normally it is an entity in the Network layer), the LLC appends its header and passes the composited data unit to MAC, which then appends its header and trailer to constitute a MAC frame. This frame is captured by a bridge, which then checks the destination address field of the frames on the LAN. If the MAC layer protocol is different from that associated with the destination LAN, the bridge replaces the MAC fields with the new MAC fields which are mapped from the source MAC fields to the destination MAC fields. Otherwise the bridge relays the MAC fields intact to the destination LAN.

However, on account of the dissimilarity between the two networks (XLNET and TMS-IBM Token Ring) of higher layers, a bridge implementation is not a viable solution.

Fig. 4.3 Bridge Architecture

Fig. 4.4 Interconnection of X.25 Network vinX.75

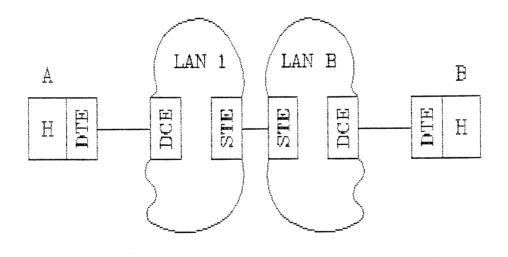

4.3.2 X.75

The X.75 standard was developed by CCITT as a supplement to X.25 [29,30,31]. It is designed for use between public X.25 networks and is not likely to be used as an interface between public and private networks. However, it could also be used to connect a collection of private X.25 networks in an internet that does not include public networks. It provides a connection-oriented service.

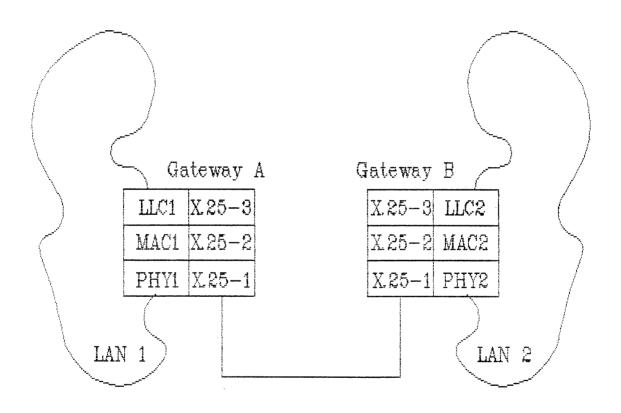

The transmission of a packet between two stations located in different LANs can be explained with reference to Fig.4.4. As shown, X.25 specifies an interface between a host equipment (data terminal equipment, DTE) and a network equipment (data circuit-terminating equipment, DCE), and X.75 uses a specific term for the network interface--signalling terminal exchange (STE) that acts as DCE-level gateways to connect two X.25 networks.

Station A sends an X.25 data packet to its DCE with the virtual circuit number that it associates with a connection to B. This packet is transmitted via LAN 1 to an STE. The STE uses the same format (Fig. 4.5), but with a modified virtual circuit number and flow control information for the appropriate STE-STE virtual circuit. The receiving STE then sends the packet to B's DCE, which presents a packet to B with the virtual circuit number that B associates with a connection to A.

If the higher layer (above Network layer) protocols are common in the subnets of an internet system, it is possible to use the X.25 protocol to implement the internet communication, even though all the subnets do not belong to the class of an X.25 network. At the sending

end, the local protocol is translated to X.25 protocol. This in turn is converted, in the second half of the gateway, from X.25 to its protocol.

For example, as shown in Fig.4.6, whenever gateway A receives an internet packet from LAN 1, it translates the local protocols and modifies the format to those of X.25 and then forwards the reformatted packet to another gateway B. Once gateway B receives the reformatted packet, it has to translate the packet into a protocol acceptable for transmission on LAN 2. As a result, a double translation is necessary to transmit an internet packet. In this case, each gateway has to contain two sets of translators, one for transmitting internet packets; the other for receiving.

If the X.25 protocol were to be implemented here, the necessary process, the double translation, would not be an efficient way to solve the problem. Further, the present higher layer protocols are not quite identical (see Table 4.1). Therefore, the X.25-X.75 Network layer gateway protocol is not adopted in the present implementation.

#### 4.3.3 Internet Protocol (IP)

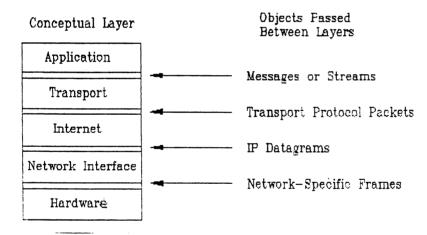

The IP is a protocol standard developed by DOD [34] as part of the DARPA Internet Project. It provides a connectionless or datagram service in the internet communications. The conceptual layer structure is shown in Fig. 4.7 [35].

| Format Group #                                         |                         |    |    |  |  |  |  |

|--------------------------------------------------------|-------------------------|----|----|--|--|--|--|

|                                                        | Channel #               |    |    |  |  |  |  |

|                                                        |                         | Ty | pe |  |  |  |  |

| Source Destination<br>Address Address<br>Length Length |                         |    |    |  |  |  |  |

| Addresses                                              |                         |    |    |  |  |  |  |

| 0                                                      | 0 0 Net Utilities Lngth |    |    |  |  |  |  |

| Network Utilities                                      |                         |    |    |  |  |  |  |

| 0 0 Facilities Length                                  |                         |    |    |  |  |  |  |

| Faclities                                              |                         |    |    |  |  |  |  |

| Data                                                   |                         |    |    |  |  |  |  |

| Form      | at | Group # |  |  |  |  |

|-----------|----|---------|--|--|--|--|

| Channel # |    |         |  |  |  |  |

| Next      | 0  | Seq (   |  |  |  |  |

| Data      |    |         |  |  |  |  |

Fig. 4.5 X.75 package formats

Fig. 4.6 X.25 protocol architecture

Fig. 4.7 The Conceptual Layer of IP

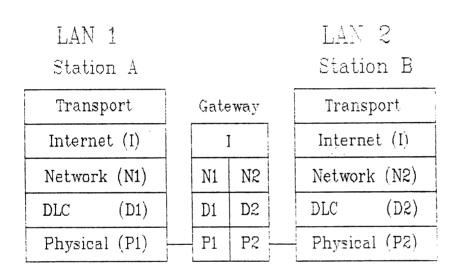

As an example, Fig. 4.8 depicts the operation of IP for data communications between station A on a LAN 1 and station B on a LAN 2. These two stations share a common transport protocol. The data to be sent by station A are encapsulated in a datagram (the datagram format shown in Fig. 4.9 [36]) in the Internet layer. Then the IP module in the station A specifies the global network address (station B) in the IP header and recognizes that the destination of the datagram is on another network. So the IP module appends to the IP datagram a LAN 1 header that contains the address of a gateway. For example, for XLNET or TMS-IBM Ring, a Network layer packet encapsulates the IP datagram to be sent to a gateway. When the packet is received by the gateway, because the packet contains an IP datagram, the LAN 1 header is stripped off, and the IP header is checked for validity. The destination IP address of a valid datagram is examined to determine whether the datagram contains control information intended for the gateway, or data intended for a station on LAN 2. Since the datagram is for station B on LAN 2 to which the gateway is directly connected, the gateway builds a new LAN 2 header for the packet and sends it to the destination, station B on LAN 2.

Fig. 4.8 Internet Prorocol

| <u>0                                    </u> | 4   | 81              | 6 19 | ) 24        | 31 |  |

|----------------------------------------------|-----|-----------------|------|-------------|----|--|

| VERS                                         | LEN | TYPE OF SERVICE | -    | OTAL LENGTH |    |  |

| IDENT FLAGS FRAGMENT OFFSET                  |     |                 |      |             |    |  |

| TIME PROTO PROTO                             |     |                 |      |             |    |  |

| SOURCE IP ADDRESS                            |     |                 |      |             |    |  |

| DESTINATION IF ADDRESS                       |     |                 |      |             |    |  |

| OPTIONS PADDING                              |     |                 |      |             |    |  |

| DATA                                         |     |                 |      |             |    |  |

| ···                                          |     |                 |      |             |    |  |

Fig. 4.9 Format of an Internet datagram, the basic unit of transfer on the Internet.

To provide reliable internet services, the vehicle also provides an internet control message protocol (ICMP) which is a required companion to IP. Basically, ICMP is used by gateways to report error and control information to internet stations and gateways. For example, when a datagram can not reach its destination, or when the lifetime of the datagram in a gateway expires, an appropriate message will be returned to the sender or gateways. Then the sender or gateways can respond appropriately.

As mentioned earlier, the fundamental requirement of using this approach is that the Transport protocols in the communicating stations must be common. Since the Transport protocols in the present subnets are not the same (see Appendix B.2), this approach is not selected for use in the our gateway.

#### 4.3.4 Protocol Translator

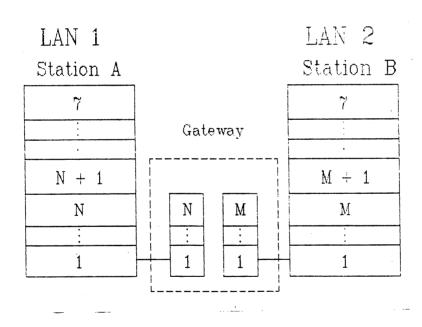

From the preceding sub-sections, we know that the limitation in using the above approaches in the proposed internet is the degree of heterogeneity between the XLNET and TMS-IBM Ring. The vehicle, Protocol translator [37, 38, 39], is able to be used to interconnect heterogeneous networks that have dissimilar layer protocols up to the Application layer (OSI, layer 7), and has been employed in some major network architectures such as interconnection between IBM's SNA and Xerox's XNS [40].

As an example, Fig. 4.10 depicts the operation of the protocol translation for communications between station A on a LAN 1 and station B on a LAN 2. In a reference model of OSI, the various layers 1,2..., N, N+1, ..., 7 are identified for each layer of architecture of station

A, and likewise the layer 1,2,..., M, M+1, ..., 7 of architecture of station B.

Whenever the gateway receives a packet sent by station A, it first of all converts from the protocols of layer N to 1 in A to those of layer M to 1 of B respectively as shown in Fig. 4.10, then forwards the translated packet to the destination station B on a LAN 2, and vice versa.

It is arguable that the most natual situation for all the cases would be M=N. However, it is more often than not the case that M >N. For example, Deaton and Hippert [43] discussed the use of an X.25 virtual circuit (M=3) instead of an SDLC link (N = 2). Although it is a bit wastful to duplicate the layer 3 function, it has the benefits of low X.25 tariffs and the ability to treat end nodes (half-gateways) adjacent to one another.

From Table 4.1, it is obvious that in our case, the protocols from the Physical Layer to the Session Layer in the XLNET are different from those in the TMS-IBM Token Ring. Therefore, it is necessary to use the approach for our internet. The number N is given to represent the Session Layer in LAN 1, and the number M is given to represent the Session Layer in LAN 2. From the OSI protocol, N is equal to M. It is seen that the layers involved in the protocol conversion should be from the Session layer to the Physical Layer. However, as a part of the implementation, the shared memory scheme (see later) is installed at the level of the Network Layer of an intermediary or a gateway for the internet communication. Then, an internet packet is not physically transmitted and received from the Physical Layer of the gateway but

Fig. 4.10 Protocol Translator

from the Network Layer instead. Therefore, the layers involved in the protocol conversion are just the Transport Layer and Session Layer as shown in Fig. 4.11. Details of the scheme are given in section 4.3.4.1 and chapter 5.

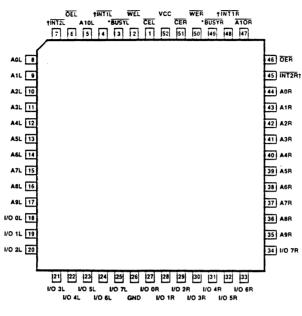

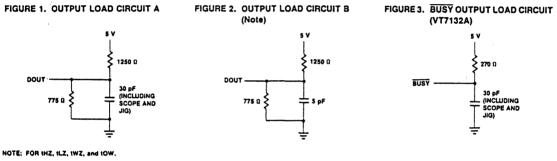

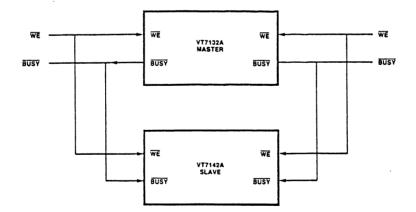

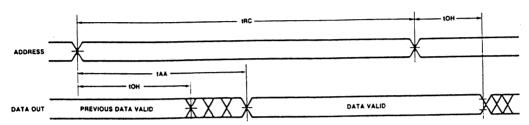

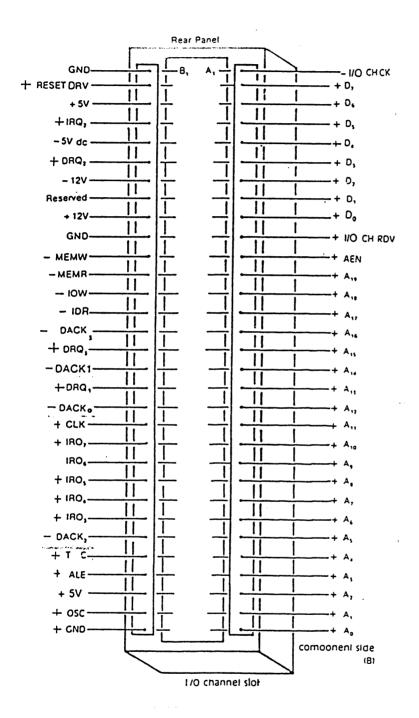

#### 4.3.4.1 Shared Memory Scheme

By the use of the characteristics of the dual-port RAM, the two separate I/O ports that each allows independent access to read or write to any location in the memory, this kind of memory can be employed as a physical path in the internet communication.

Once a half-gateway in a LAN recognizes a packet as an internet packet in its Network Layer, it puts the packet into the proper location of the memory through one I/O port. Then, the half-gateway sends an advice by an interrupt signal to its partner, the other half-gateway in the other LAN. At the other side, once the partner recognizes the advice, it is ready to pick the packet up from the memory through the other I/O port.

This approach employed in the internet system has the following merits:

1. The transmission delay in the medium can be considered to be equal to the memory access time. What is the value of the memory access time? The answer depends on what kind of the memory we choose. In our case, the memory access time of the dual-port RAM (see Appendix C) we used is just 45 nanoseconds. Meanwhile, the form of a packet transmission in the parallel 8 line ribbon cable is byte

Fig. 4.11 Protocol translation by using the shared memory scheme.

by byte. The maximum transmission speed can be up to 8 bits/45 nanoseconds which is about 178 Mbits/sec. Of course, the speed is significantly faster than RS-232C 9.6 Kbits/sec. in the traditinoal way, that is, in the form of bit by bit transmission.

2. Since the main functionality of the Network Layer is to route a packet through a proper path to its destination, if the shared memory scheme is employed in the layer, an internet packet is not necessary to be served by the DLC Layer and Physical Layer of a half-gateway to the other half-gateway then its destination, but directly by the Network Layer through the dual-port RAM instead. By this way, the protocol conversions for the DLC Layer and Physical Layer are delimited. Meanwhile, the time delay spent on processing an internet packet in the DLC Layer and Physical Layer is saved. So the transmission speed for the internet packet can be increased. Concurrently, the cost of the physical equipment for the protocol conversion in the Physical Layer (e.g. the line code transformer might be needed for the translation of line code from the Biphase-S code to the Differential Manchester code, and vice versa.) is saved as well.

The drawback is that a short physical distance between the two subnets is required. Since an internet packet is transmitted byte by byte in a parallel form, the signal by parallel transmission cannot suffer large distortion incurred in the long distance transmission. However, the extension of the distance between the two subnets is still possible by using the signal repeaters in the appropriate location to supply the signal in the path.

#### 4.4 <u>Communication Services</u>

The communication service in a network or an internetwork is chosen from one of two services. The first service is connectionoriented; the second is connectionless. A brief description of each service will be presented in the following paragraphs.

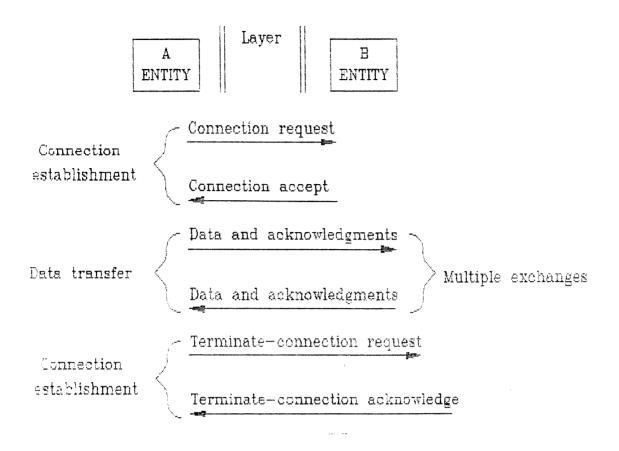

As shown in Fig. 4.12, a connection-oriented service provides a substantial amount of protection for the user data. Most connection services have three phases which are "Connection establishment", "Data transfer" and "Connection termination".

The connection must be established before data transfer takes place. Typically, to achieve the agreement to exchange data between two entities, one entity issues a connection request to the other, then the receiving entity either accepts or rejects the request. The establishment phase can be used to negotiate quality of service or operations, such as timing restriction or the length of a packet in the data transfer.

Following connection establishment, the data transfer phase is entered. During this phase, both control and data information is exchanged. Finally, a termination request is sent by one of the two entities which wants to terminate the connection.

Fig. 4.12 Connection-oriented Services

Fig. 4.13 Connectionless services

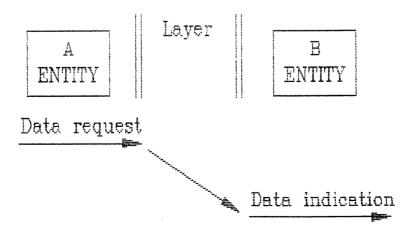

In contrast, connectionless services (sometimes called datagram services ) are simple to implement in that the user is not provided with any form of response to a transaction, each transaction is independent of previous transactions and the user transmits data without prior coordination. As shown in Fig. 4.13, by using the connection-less service, the variety of service protocol is reduced; only one protocol over all subnetworks. However, duplicate messages can easily result from Data-link or Network layer retransmissions. Messages may also be discarded due to corruption of data or lack of buffer space. Therefore, frequently connection-oriented services are preferred.

From the above, it is clear that each service has its merits and demerits. But, based on the considerations given below we settle for a connectionless service. The following are the reasons:

(1) In our task, the integrated communications have critical realtime requirements for synchronous services, such as voice. Since packets must be delivered within a strictly bounded time, they can not tolerate the delay penalties associated with the sequence and flow control which might be incurred by the use of the connection-oriented services.

(2) If the connection-oriented technique were employed, the gateway would be more complex. For meeting the requirements of the connection-oriented service, the gateway would not only have to preallocate the space for the table but also process it for maintaining connection state information. Furthermore, the connection-oriented services incur more protocol overhead traffic than connectionless ones. These would result in significant process delay in the data transfer

through the gateway. Therefore, the connectionless services are more suitable for real-time communication (e.g. voice).

(3) The reliability of a connection-oriented service is obtained at the expense of performance. According to Meister [41], the throughput provided by connection-oriented services can be expected to be lower than by connectionless ones, since the connection-oriented services are more complex and need more protocol overhead traffic than connectionless ones.

(4) Furthermore, in both subnets, the network service (layer 1-3), which is common to all applications, is designed to provide an efficient and reliable connectionless network service to the connection-oriented Transport Layer which has functions, such as error control and flow control, to provide connection-oriented services. Due to the considerable amount of protocol architecture involved in both subnets, it is not really necessary to use the connection-oriented services in the internetworking communications.

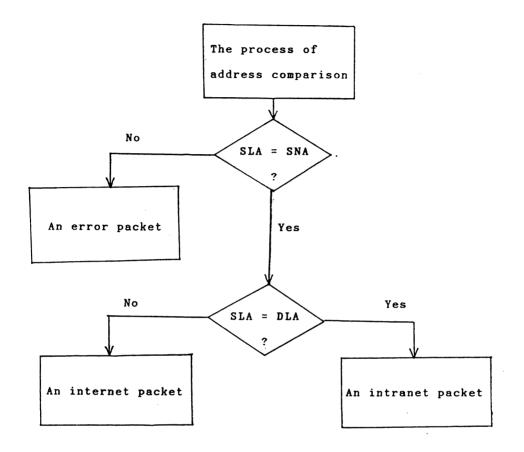

#### 4.5 Addressing

In both XLNET and TMS-IBM Token Ring, the Network layers are not designed with internetworking in mind. For interconnecting them and transmitting messages across each network boundary, it is necessary to add this function to the Network layer. Hence the addressing must be re-considered.

In a datagram network, every message contains source and destination station addresses. The station address is 8 bits long in XLNET, while it is 48 bits long in TMS-IBM Token Ring. Whenever a station is connected to its own LAN, it is assigned a unique and specific length (8 bits in XLNET; 48 bits in TMS-IBM) address. Before an XLNET station is connected to the ring, its address must be assigned by the station user, otherwise it is considered as a repeater in the link. An XLNET station's address can only be changed by the user while it is in the operation mode of a repeater. For TMS-IBM Ring, a station's address must be assigned by the station user, otherwise it is not able to be connected to the link.

For communicating in an internetworking environment, there are two choices for addressing stations:

(1) Unique Global Address

That is, there is a unique identifier for each station in the internet. This implies that a gateway would need to derive subnet addresses from station addresses. The technique has been proposed by the developers of Ethernet [42]. The principal advantage of this approach is that it is able to make stations portable. That means it permits stations to move physically from one network to another without changing stations addresses. The primary disadvantage is that very large routing tables are needed, indexed by station address to determine the subnet and gateways to be used to reach the station.

If this technique were to be chosen, it would be necessary to change the present and simpler subnet addressing scheme and substantially effect the subnet independence. For this reason, it will not be adopted for our application.

(2) Network Specific Address

A gateway receives an internet packet with a reference in the form "subnet.station", where "subnet" is a subnet address. The

"station" component needs only be unique within the subnet, although the combined address is globally unique. The "subnet" is used for routing to the final subnet, thereafter the "station" is used for identifying the destination station in the subnet. The Darpa IP [34] uses this addressing scheme. The primary shortcoming [42] of this addressing mode is that additional administrative procedures are needed to assign station addresses within a subnet, and possibly translate different length station addresses within a gateway.

#### 4.6 Segmentation and Reassembly

In general, subnets (no matter how heterogeneous) within an internet have different maximum (and sometimes minimum) packet sizes. Thus gateways may need to segment incoming datagrams into smaller pieces before transmitting into the next network. This process is called segmentation, or fragmentation.

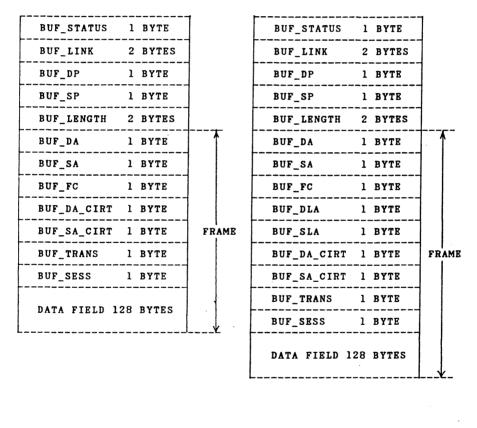

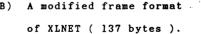

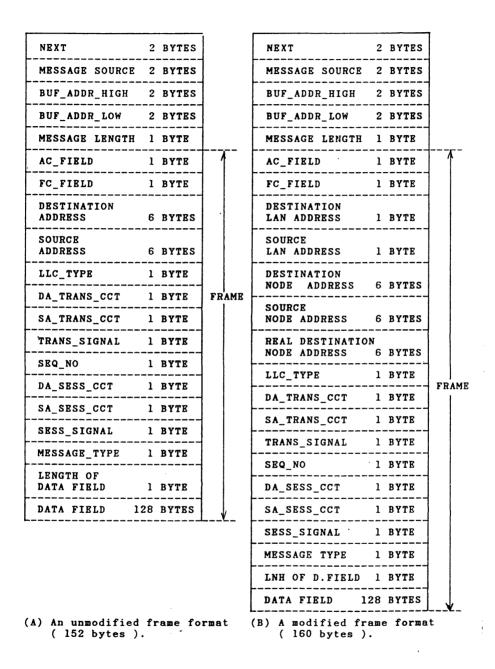

With the proposed internet, although the packet size defined in the two non-homogeneous subnets is not the same (160 bytes in TMS-IBM Token Ring; 137 bytes in XLNET), the size of data fields is identical (128 bytes). Although the fragmentation could be implemented in this case, as explained above, it would result in an inefficient and unnecessarily complex procedure. By using the shared memory scheme mentioned in section 4.3.4.1 and chapter 5 to implement the protocol translation and frame reformation, the transfer of the user message in the data fields from an XLNET packet to an TMS-IBM Ring packet is executed as the exchange of the memory location, and vice versa. Then, the segmentation and the later reassembly are not necessary. The shortcomings of the segmentation and reassembly are:

(1) As the following fields are required in the protocol control header to support segmentation and reassembly, the smaller is the block, the greater is the percentage overhead.

a. More Bit.

This indicates whether the packet is part of a segmented service data unit or not. The last packet of the data unit has the bit cleared.

b. Data Unit Identifier.

This identifies to which datagram a segment belongs.

c. Offset.

This provides the position of a segment in the original datagram to enable reassembly and detect lost segments.

d. Total Length

This indicates the length of the segmented datagram and allows reservation of buffer space.

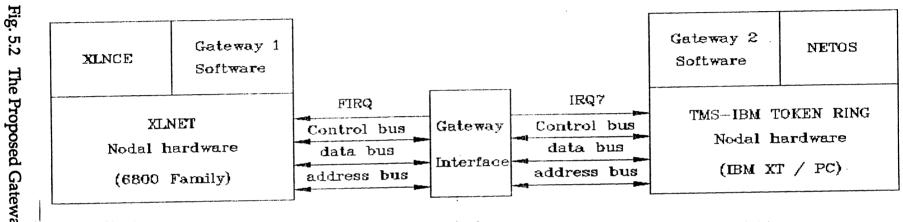

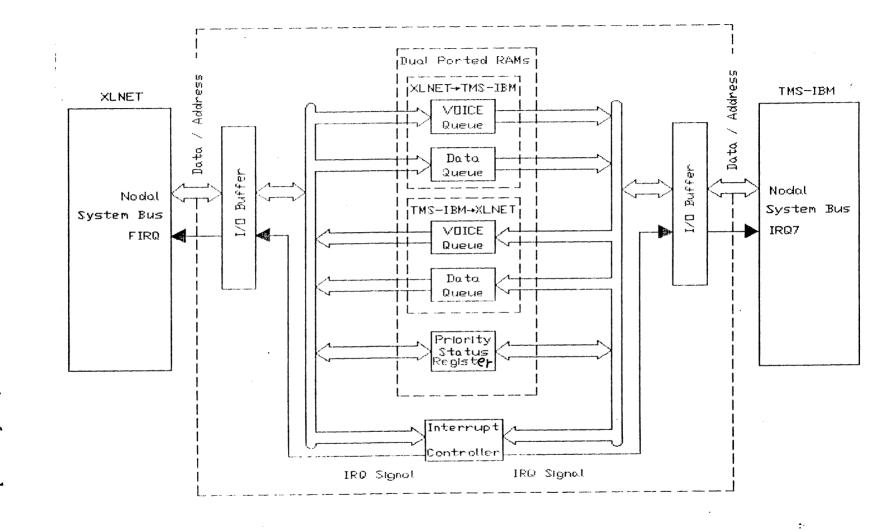

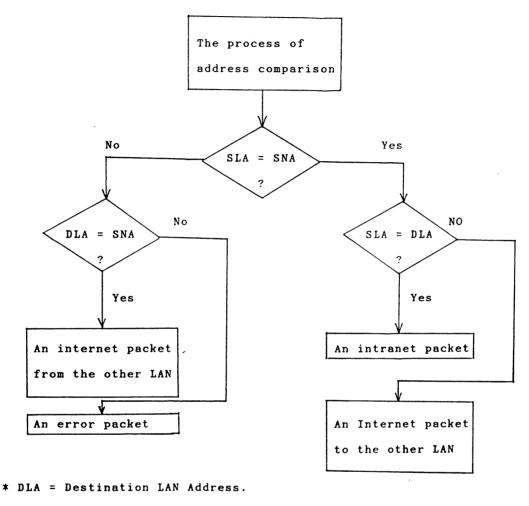

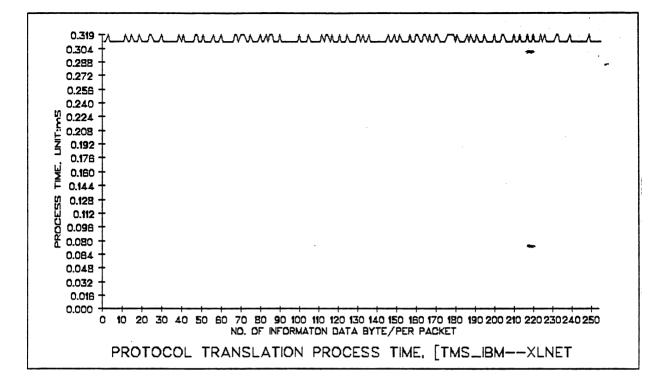

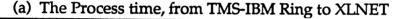

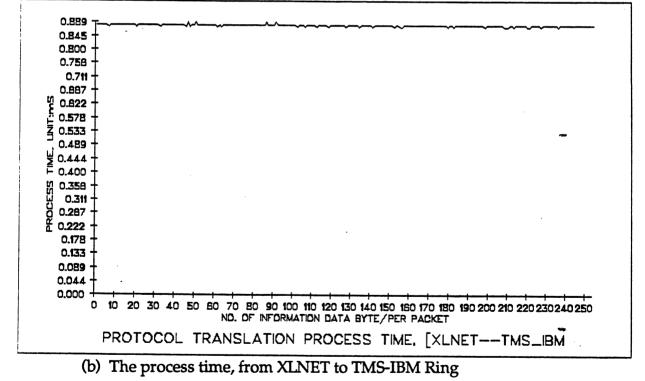

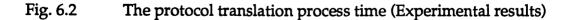

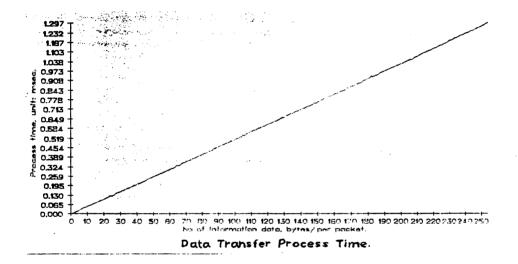

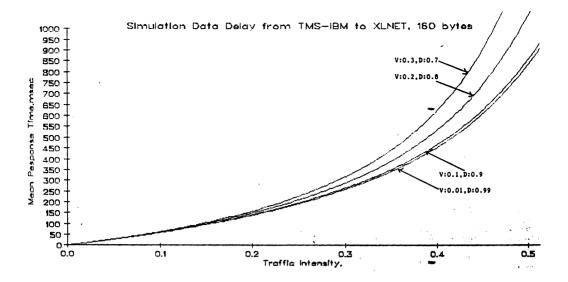

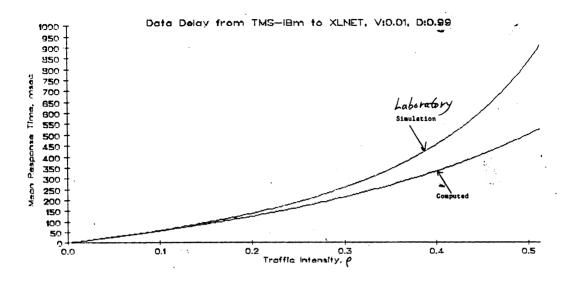

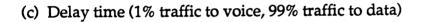

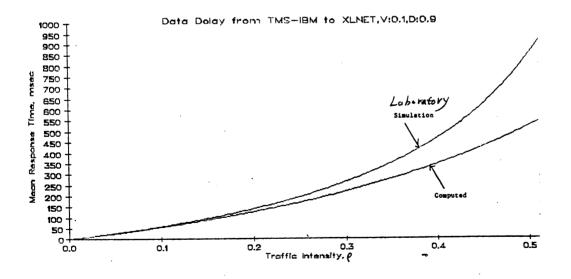

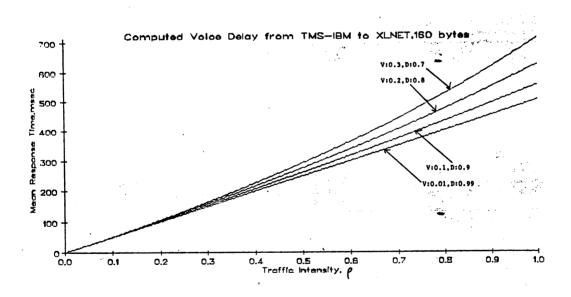

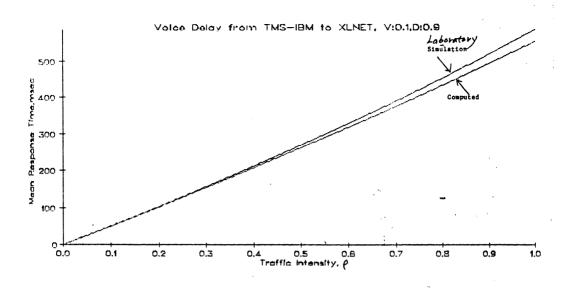

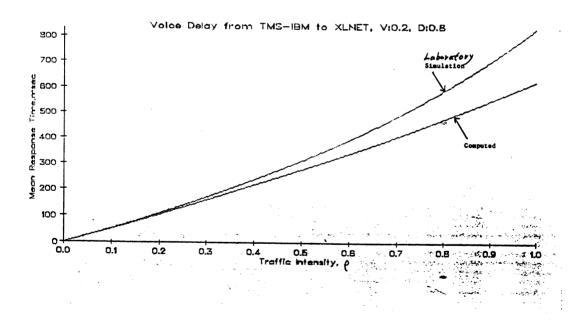

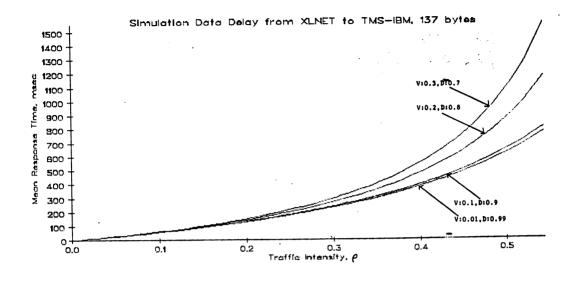

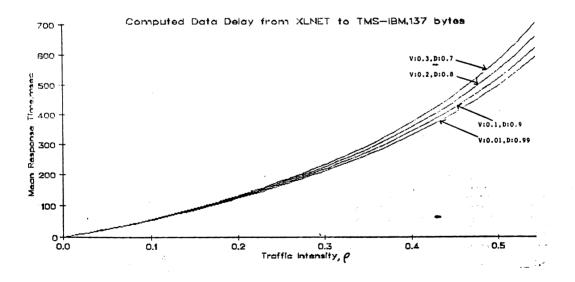

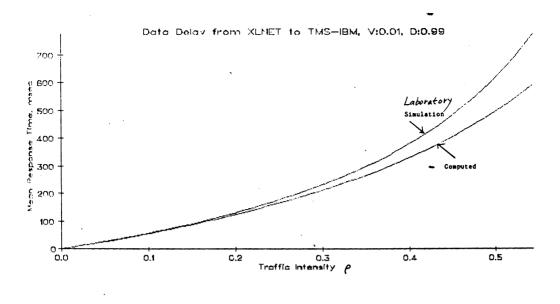

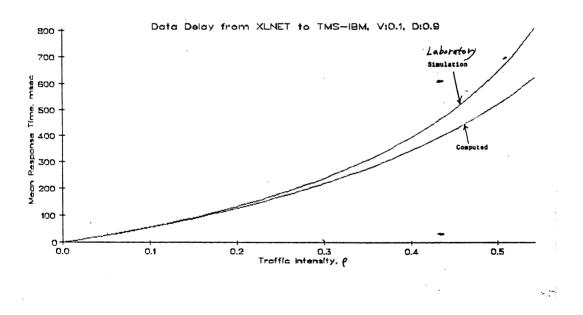

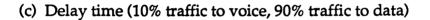

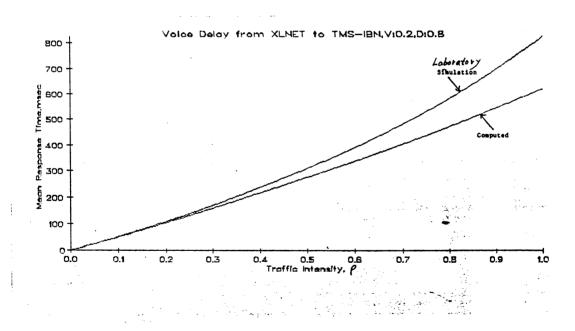

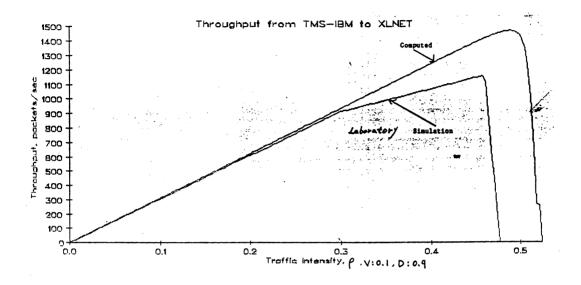

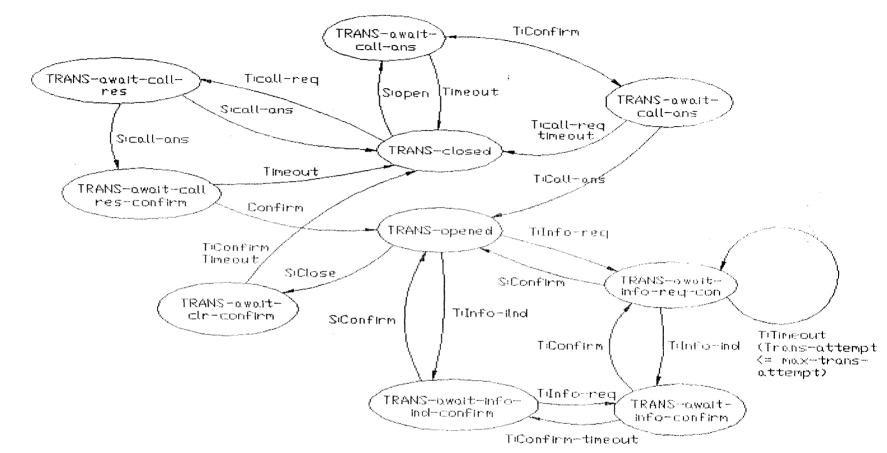

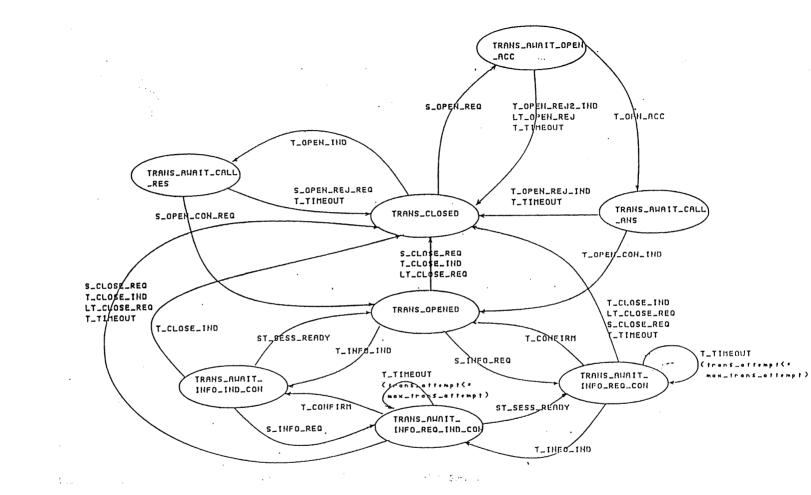

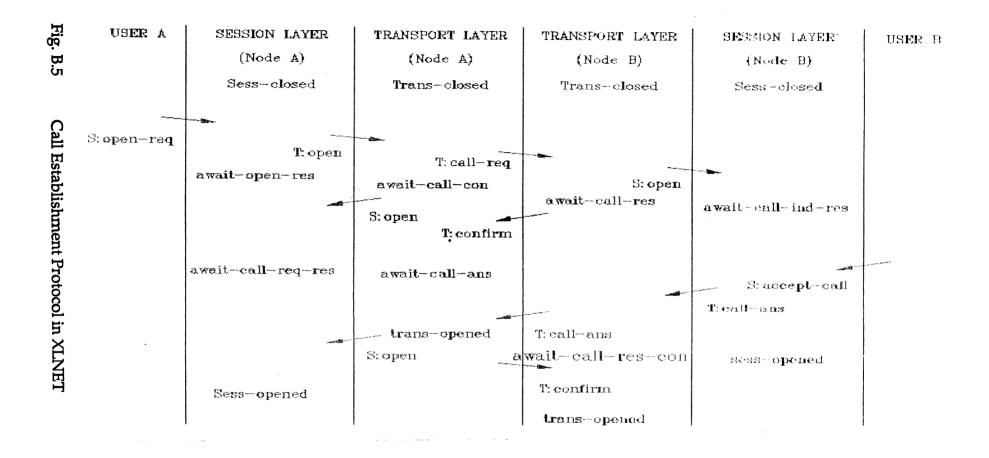

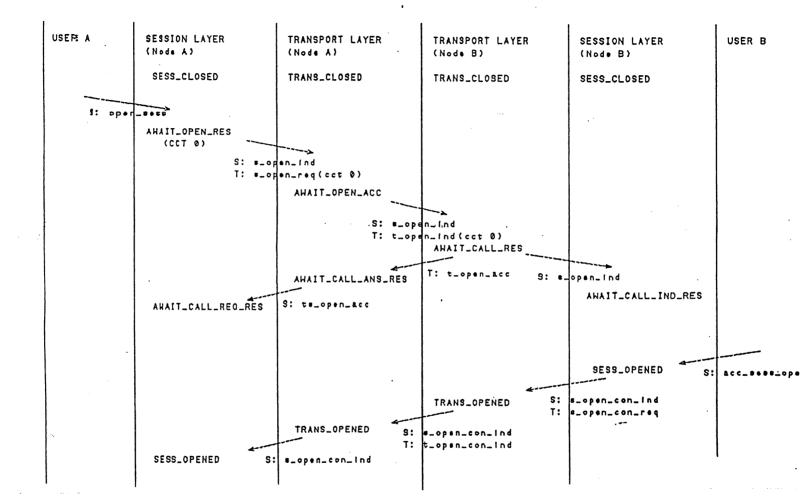

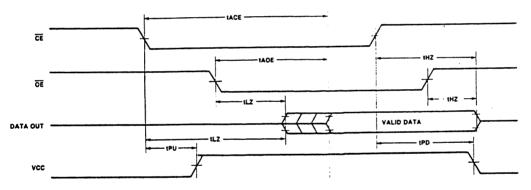

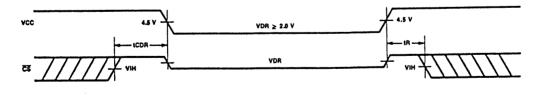

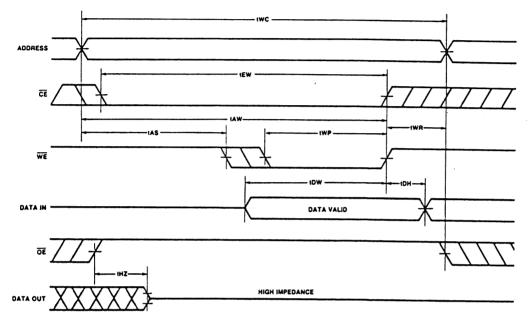

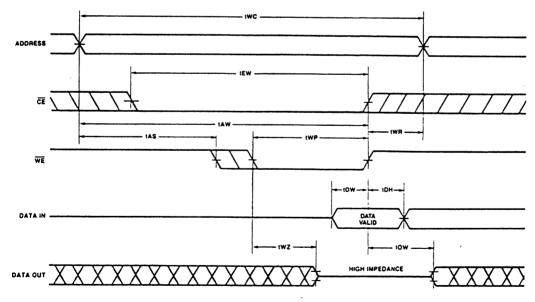

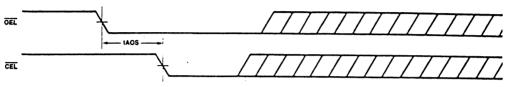

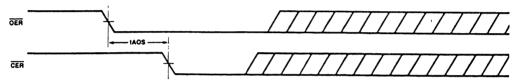

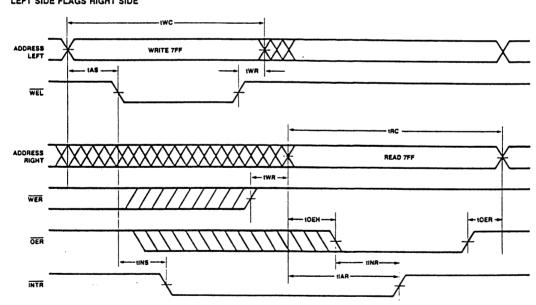

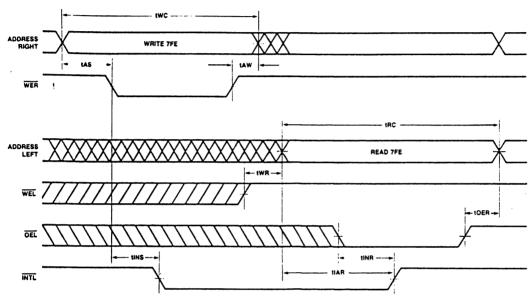

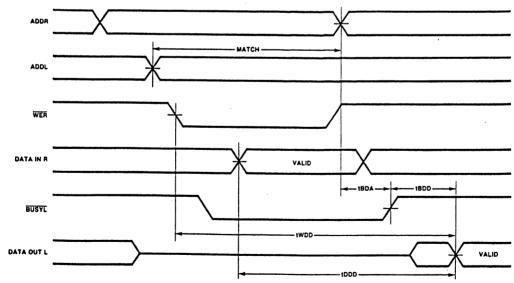

(2) Doing the process of segmentation will increase the gateway process time, and , therefore, delay.