Applying FPGA Runtime Reconfiguration to Multi-Hash Proofof-Work Algorithms

**Author:** Wu, Tong

Publication Date: 2022

DOI: https://doi.org/10.26190/unsworks/25287

# License:

https://creativecommons.org/licenses/by/4.0/ Link to license to see what you are allowed to do with this resource.

Downloaded from http://hdl.handle.net/1959.4/101580 in https:// unsworks.unsw.edu.au on 2024-05-03

# Applying FPGA Runtime Reconfiguration to Multi-Hash Proof-of-Work Algorithms

# Tong Wu

A thesis in fulfilment of the requirements for the degree of

Master of Philosophy

School of Computer Science and Engineering

Faculty of Engineering

The University of New South Wales

October 2022

#### ORIGINALITY STATEMENT

✓ I hereby declare that this submission is my own work and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at UNSW or any other educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom I have worked at UNSW or elsewhere, is explicitly acknowledged in the thesis. I also declare that the intellectual content of this thesis is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.

#### COPYRIGHT STATEMENT

✓ I hereby grant the University of New South Wales or its agents a non-exclusive licence to archive and to make available (including to members of the public) my thesis or dissertation in whole or part in the University libraries in all forms of media, now or here after known. I acknowledge that I retain all intellectual property rights which subsist in my thesis or dissertation, such as copyright and patent rights, subject to applicable law. I also retain the right to use all or part of my thesis or dissertation in future works (such as articles or books).

For any substantial portions of copyright material used in this thesis, written permission for use has been obtained, or the copyright material is removed from the final public version of the thesis.

#### AUTHENTICITY STATEMENT

🗹 I certify that the Library deposit digital copy is a direct equivalent of the final officially approved version of my thesis.

C The candidate has declared that some of the work described in their thesis has been published and has been documented in the relevant Chapters with acknowledgement.

A short statement on where this work appears in the thesis and how this work is acknowledged within chapter/s:

Chapter 5 is partially based on our research that was published in FCCM2022. I have acknowledged this in the first chapter.

#### **Candidate's Declaration**

I declare that I have complied with the Thesis Examination Procedure.

# Acknowledgement

I would like to express my immense thanks to my supervisor, Prof. Diessel, for his invaluable advice, support, and patience through my masters research.

I would also like to thank my parents, Lucy and Davis, and my girlfriend, Maddie, for their unending love and support, without which I would not have been able to embark on this work.

# Abstract

In the cryptocurrency mining field, algorithms have been developed to discourage the development of ASICs that greatly out-compete general-purpose hardware in both performance and power efficiency. A class of algorithms that claims to be ASIC-resistant is the class of randomised multi-hash proof-of-work algorithms, such as X16R. For these algorithms, the result of one iteration depends on the chained application of several randomly selected hash functions, which has the effect of disadvantaging fixed-function ASICs due to their inflexibility. FPGAs lie between GPUs and ASICs in terms of raw performance and flexibility. We investigate the use of FPGAs for this type of proof-of-work, in particular, by leveraging the ability of modern FPGAs to quickly reconfigure at runtime. We implemented a design that runs the X16R algorithm by partially reconfiguring the FPGA for every hash function in the chain and processing the data in batches. We show that our system achieves better performance when compared to GPUs that are manufactured on the same semiconductor process technology node, while being several times more power efficient. The two key takeaways from this work are that FPGA runtime reconfiguration can be used to effectively accelerate algorithms for which the demand for different processing elements changes over time, and that proof-of-work algorithm designers should consider FPGAs as a class of computing device that is separate from fixed-function ASICs.

# Contents

| A | Acknowledgement 3 |                                            |       |

|---|-------------------|--------------------------------------------|-------|

| A | bstra             | ract                                       | 4     |

| 1 | Intr              | troduction                                 | 10    |

|   | 1.1               | Overview                                   |       |

|   | 1.2               | 2 Contributions                            |       |

|   | 1.3               | B Publications and awards                  |       |

| 2 | Bac               | ackground                                  | 13    |

|   | 2.1               | Cryptocurrency mining                      |       |

|   |                   | 2.1.1 Proof-of-Work                        |       |

|   |                   | 2.1.2 Pooled mining                        |       |

|   |                   | 2.1.3 Evolution of mining hardware         |       |

|   |                   | 2.1.4 ASIC-resistance                      |       |

|   | 2.2               | P FPGA runtime reconfiguration             |       |

|   |                   | 2.2.1 FPGA hardware                        |       |

|   | 2.3               | B Related Work                             |       |

|   |                   | 2.3.1 Applications of runtime reconfigurat | tion  |

|   |                   | 2.3.2 Runtime reconfiguration methodolog   | gy 24 |

| 3 | $\mathbf{Des}$ | ign ex                                                                                                                               | ploration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26                                                                                                                                 |

|---|----------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   | 3.1            | X16R                                                                                                                                 | algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26                                                                                                                                 |

|   |                | 3.1.1                                                                                                                                | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26                                                                                                                                 |

|   |                | 3.1.2                                                                                                                                | Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27                                                                                                                                 |

|   | 3.2            | Static                                                                                                                               | design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28                                                                                                                                 |

|   | 3.3            | Dynar                                                                                                                                | nic full chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29                                                                                                                                 |

|   | 3.4            | Time-s                                                                                                                               | sliced dynamic sub-chains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                                                                 |

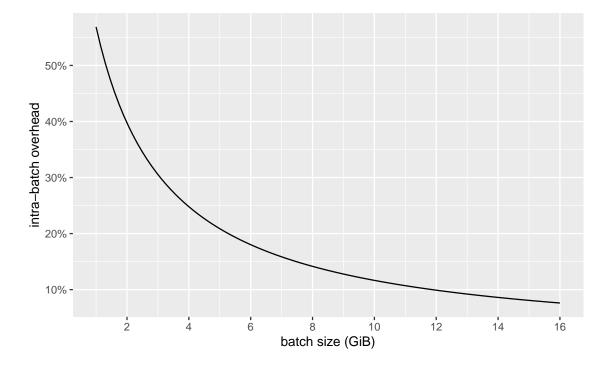

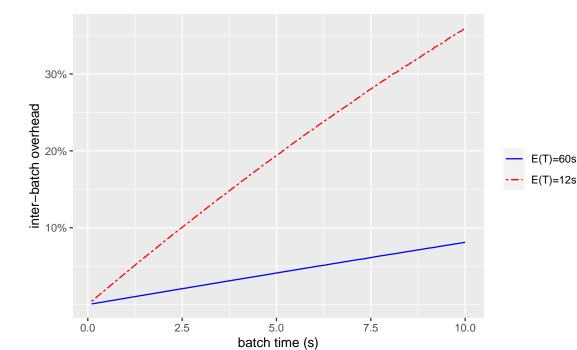

|   | 3.5            | Overh                                                                                                                                | eads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                                                                                                                                 |

|   |                | 3.5.1                                                                                                                                | Intra-batch overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31                                                                                                                                 |

|   |                | 3.5.2                                                                                                                                | Inter-batch overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32                                                                                                                                 |

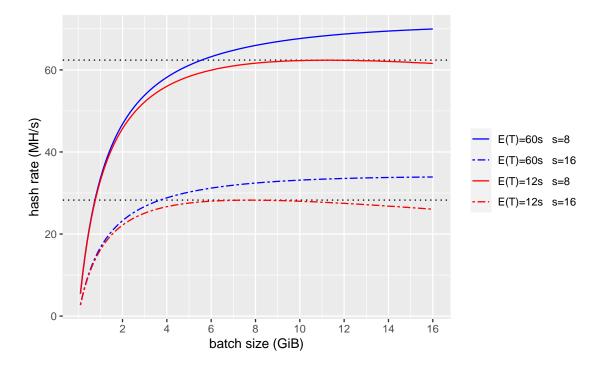

|   |                | 3.5.3                                                                                                                                | Estimated performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34                                                                                                                                 |

| 4 | Has            | h func                                                                                                                               | tions implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36                                                                                                                                 |

|   |                |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

|   | 4.1            | Is HLS                                                                                                                               | S auto-pipelining competitive with handcrafted RTL?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36                                                                                                                                 |

|   | 4.1            | Is HLS<br>4.1.1                                                                                                                      | S auto-pipelining competitive with handcrafted RTL?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                    |

|   | 4.1            |                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                                                                                                 |

|   | 4.1            | 4.1.1                                                                                                                                | Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37<br>38                                                                                                                           |

|   | 4.1            | 4.1.1<br>4.1.2                                                                                                                       | Languages       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 37<br>38                                                                                                                           |

|   | 4.1            | <ul><li>4.1.1</li><li>4.1.2</li><li>4.1.3</li></ul>                                                                                  | Languages       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . | 37<br>38<br>39<br>40                                                                                                               |

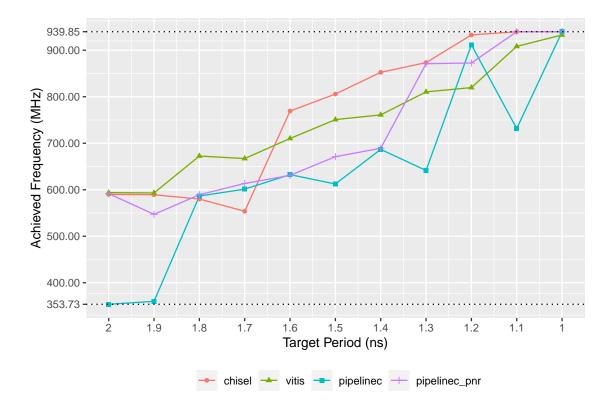

|   | 4.1            | <ul><li>4.1.1</li><li>4.1.2</li><li>4.1.3</li><li>4.1.4</li></ul>                                                                    | Languages          Designs evaluated          How results were collected          AES results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>37</li> <li>38</li> <li>39</li> <li>40</li> <li>40</li> </ul>                                                             |

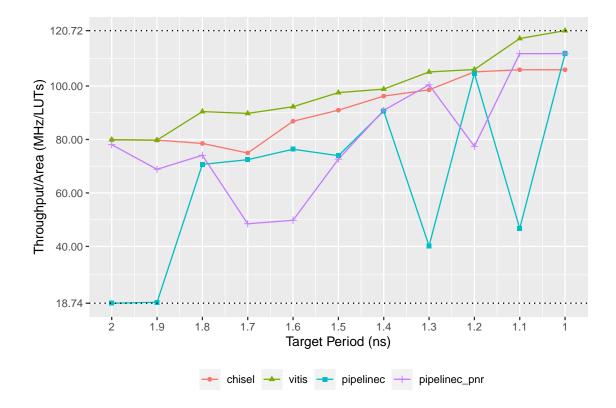

|   | 4.1            | <ul> <li>4.1.1</li> <li>4.1.2</li> <li>4.1.3</li> <li>4.1.4</li> <li>4.1.5</li> </ul>                                                | Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ol> <li>37</li> <li>38</li> <li>39</li> <li>40</li> <li>40</li> <li>42</li> </ol>                                                 |

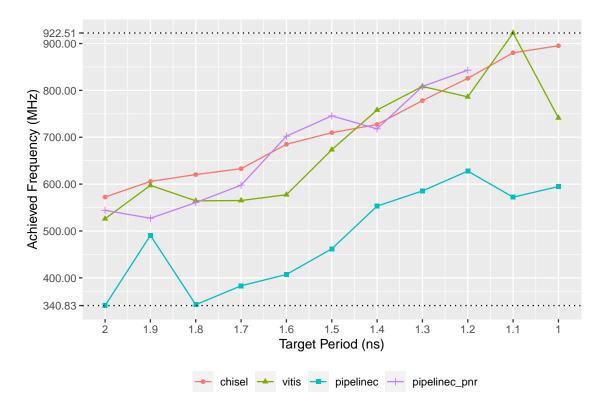

|   | 4.1            | $\begin{array}{c} 4.1.1 \\ 4.1.2 \\ 4.1.3 \\ 4.1.4 \\ 4.1.5 \\ 4.1.6 \\ 4.1.7 \end{array}$                                           | Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>37</li> <li>38</li> <li>39</li> <li>40</li> <li>40</li> <li>42</li> <li>44</li> </ul>                                     |

|   |                | $\begin{array}{c} 4.1.1 \\ 4.1.2 \\ 4.1.3 \\ 4.1.4 \\ 4.1.5 \\ 4.1.6 \\ 4.1.7 \end{array}$                                           | Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>37</li> <li>38</li> <li>39</li> <li>40</li> <li>40</li> <li>42</li> <li>44</li> <li>45</li> </ul>                         |

|   |                | <ul> <li>4.1.1</li> <li>4.1.2</li> <li>4.1.3</li> <li>4.1.4</li> <li>4.1.5</li> <li>4.1.6</li> <li>4.1.7</li> <li>Hash of</li> </ul> | Languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>37</li> <li>38</li> <li>39</li> <li>40</li> <li>40</li> <li>42</li> <li>42</li> <li>44</li> <li>45</li> <li>45</li> </ul> |

# 5 X16R implementation

|   | 5.1 | Target hardware                        | 49 |

|---|-----|----------------------------------------|----|

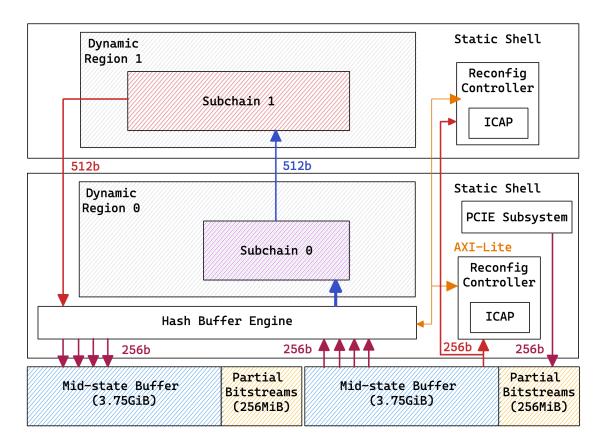

|   | 5.2 | System design                          | 50 |

|   |     | 5.2.1 PCIe subsystem                   | 51 |

|   |     | 5.2.2 Reconfiguration controller       | 51 |

|   |     | 5.2.3 Hash buffer engine               | 53 |

|   | 5.3 | Single function per reconfiguration    | 55 |

|   | 5.4 | Multiple functions per reconfiguration | 56 |

|   | 5.5 | Multi-SLR scaling                      | 57 |

|   | 5.6 | Results                                | 57 |

| 6 | Con | clusion                                | 61 |

|   | 6.1 | Summary                                | 61 |

|   | 6.2 | Discussion                             | 62 |

|   | 6.3 | Future work                            | 63 |

| A | App | pendix A                               | 70 |

|   | A.1 | Ethash                                 | 70 |

|   | A.2 | RandomX                                | 71 |

# List of Figures

| 2.1 | Bitcoin network hashrate                                                 | 17 |

|-----|--------------------------------------------------------------------------|----|

| 3.1 | Probability of X16R chain having a function that occurs N times, and all |    |

|     | other functions occurring at most N times $\hdots$                       | 28 |

| 3.2 | Intra-batch overhead versus batch size                                   | 32 |

| 3.3 | Inter-batch overhead                                                     | 34 |

| 3.4 | Estimated hash rate vs batch size                                        | 35 |

| 4.1 | AES: achieved frequency                                                  | 41 |

| 4.2 | AES: throughput/area                                                     | 41 |

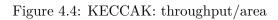

| 4.3 | KECCAK: achieved frequency                                               | 42 |

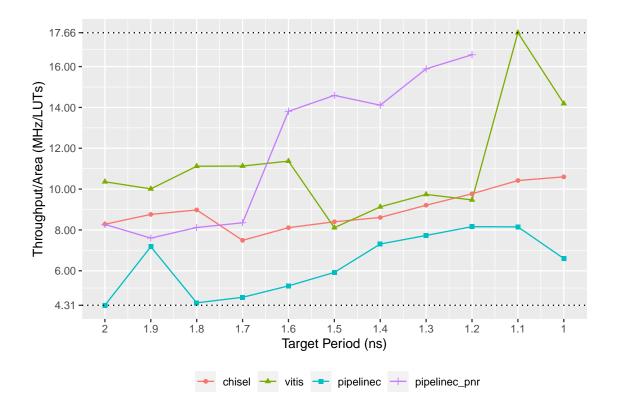

| 4.4 | KECCAK: throughput/area                                                  | 43 |

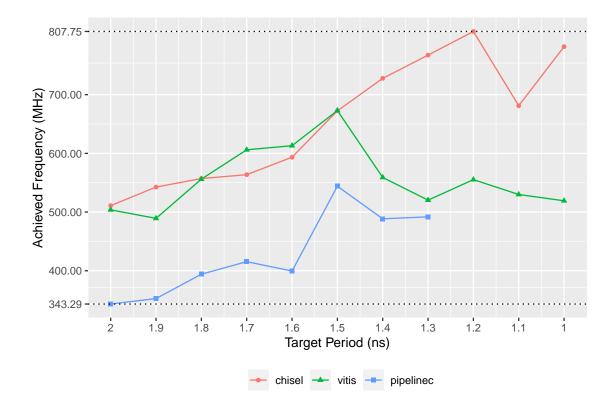

| 4.5 | GROESTL: achieved frequency                                              | 43 |

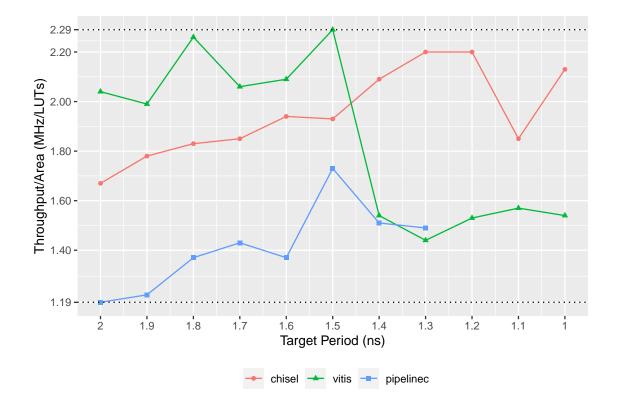

| 4.6 | GROESTL: throughput/area                                                 | 44 |

| 5.1 | ASUS B250 Mining Expert                                                  | 50 |

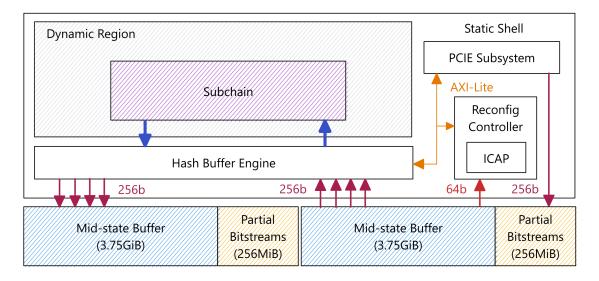

| 5.2 | System overview                                                          | 51 |

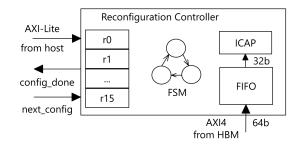

| 5.3 | Reconfiguration controller                                               | 52 |

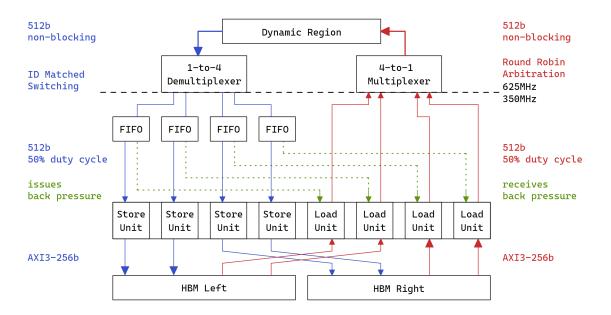

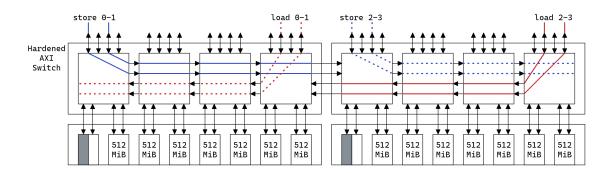

| 5.4 | Hash buffer engine                                                       | 54 |

| 5.5 | HBM channel configuration                                                | 54 |

| 5.6 | Two SLR system                                                           | 58 |

# List of Tables

| 2.1 | Bitcoin block structure         | 14 |

|-----|---------------------------------|----|

| 2.2 | Bitcoin block header            | 14 |

| 4.1 | Hash core resource utilization  | 48 |

| 5.1 | X16R performance and efficiency | 59 |

# Chapter 1

# Introduction

## 1.1 Overview

Blockchain based cryptocurrencies, such as Bitcoin, are distributed ledgers that require many distributed bookkeepers in order to function. To protect the blockchain from spam, a proof-of-work based consensus protocol is used to reach an agreement on the current state of the ledger. Proof-of-work (PoW) algorithms require the bookkeepers to perform some work, which usually involves executing a hashing algorithm many times. The bookkeepers doing this work are referred to as miners. Initially, on cryptocurrencies such as Bitcoin, miners were able to use commodity hardware such as CPUs and GPUs to perform proof-of-work. However, over time, Application-Specific Integrated Circuits (ASICs) were developed that offered an increase of orders of magnitude in performance and energy efficiency over CPUs and GPUs. Today, many cryptocurrencies try to introduce ASICresistance to their proof-of-work algorithms in order to maintain the viability of CPU or GPU mining. One of these, ASIC-resistance methods, relies on multi-hash PoW algorithms that chain together several different hash functions to ensure that there is additional complexity when being implemented in hardware. Some multi-hash PoW algorithms, such as X16R, also require the sequence of hash functions being executed to be randomly selected at the start of every time window.

Field-Programmable Gate Arrays (FPGAs) are semiconductor devices that are based around a reconfigurable matrix of lookup tables (LUTs), flip-flops (FFs) and interconnects. They are capable of implementing any boolean logic circuit (given that the circuit fits within the number of LUTs and FFs available) and are often used to accelerate algorithms that are ill-suited for traditional processors (CPUs and GPUs). FPGAs differ from ASICs in that they are reconfigurable, allowing a single device to be re-purposed for many different applications, while sacrificing some performance and energy efficiency. It is also possible to reconfigure portions of the FPGA at run time, allowing for the user to change the functionality without a reboot. This feature is often referred to as dynamic partial reconfiguration (DPR) or runtime reconfiguration.

Multi-hash chain PoW algorithms that randomize the order of hash functions have the effect of introducing a significant overhead within ASICs and static FPGA implementations. This research aims to investigate the use of FPGA runtime reconfiguration to improve the performance of these types of algorithms, by allocating FPGA resources as needed by the algorithm during runtime.

# **1.2** Contributions

This thesis makes the following contributions:

- 1. A design exploration of potential FPGA-based designs for computing X16R and multi-hash PoW algorithms in general. We find that a static, fixed-function design is impractical to implement on the current generation of FPGAs and would be bottlenecked in performance due to the inherent properties of the X16R algorithm. We consider two dynamically reconfigurable architectures, dynamic full chain, and time-sliced dynamic sub-chains, which allow for the elimination of the bottlenecks apparent in the static design. We determine that the time-sliced approach can be more practically implemented.

- 2. An analysis of the overheads within the time-sliced dynamic sub-chains approach to X16R and the expected performance. We find that our time-sliced approach to X16R does not lose much efficiency for blockchains with lower average block intervals, even as low as 12 seconds.

- 3. A comparison of the maximum clock frequency achieved by using the auto-pipelining features of PipelineC, Vitis HLS, and hand-optimized RTL. We find that Vitis HLS

performs comparably or better than hand-optimized RTL on small to medium designs in general, and also when below 666MHz for large designs. PipelineC also performs well for small and medium designs, however, the long compile times required make it infeasible to use for large designs.

4. Implementations of three variants of our time-sliced dynamic sub-chains architecture, SFR, MFR, and SFR2. These achieved several times better power efficiency than GPUs, even when comparing to GPUs that were manufactured on a more recent technology node. Therefore, we demonstrate the utility of FPGA runtime reconfiguration in speeding up and making possible the computation of multi-hash PoW algorithms on widely available FPGA hardware.

# **1.3** Publications and awards

During the course of our research we published a portion of our work on the design and implementation of our time-sliced approach to computing X16R. Specifically, we submitted our Single-Function-per-Reconfiguration (SFR) design variant to **The 30th IEEE International Symposium On Field-Programmable Custom Computing Machines** conference (FCCM2022) as a 4-page short paper where it was **accepted**. My supervisor and co-author provided advice regarding the direction of research and editorial support.

• Wu, T. and Diessel, O., 2022. Leveraging FPGA Runtime Reconfigurability to Implement Multi-Hash-Chain Proof-of-Work. In: *The 30th IEEE International Symposium On Field-Programmable Custom Computing Machines.*

We also submitted a simplified version of our SFR2 design variant to the AMD-Xilinx **2021 Adaptive Computing Challenge** and it was **awarded second place** in the *Big Data Analytics* category.

• Fast DFX for Multi-hash Algorithms — https://www.xilinx.com/developer/ adaptive-computing-challenge/contest-2021.html

# Chapter 2

# Background

# 2.1 Cryptocurrency mining

#### 2.1.1 Proof-of-Work

Cryptocurrencies based on blockchains are in essence distributed data structures where information is stored as ever-growing lists of transaction records, grouped into objects called blocks. Each block contains a cryptographic hash of the previous block, thus linking every block in a chain. Updates to the blockchain can only happen when a new block is added to the chain. Bitcoin is designed such that a new block is added to the chain approximately once every ten minutes. So as to allow any party to contribute, and to prevent all participants from attempting to do so at the same time, the system must choose a random participant to submit the next block. This is done by having the submitter attach a *Proof-of-Work* (PoW) along with their submission. This proof-of-work is the solution to a computationally intensive problem that everyone has a fair chance of solving and is representative of the effort they have invested. The first to find the solution and submit the new block is rewarded some freshly minted cryptocurrency (e.g. Bitcoin). Since there is a promise of reward, many are willing to expend computational power and energy to increase their chance of getting the reward. This is called mining, as it is analogous to mining for gold.

As an example, we examine the proof-of-work system for the most popular cryptocurrency, Bitcoin [23]. The data structure of a Bitcoin block is shown in Table 2.1.

| Field               | Description                          | Size      |

|---------------------|--------------------------------------|-----------|

| Block Size          | size of this block                   | 4 bytes   |

| Block Header        | other metadata                       | 80 bytes  |

| Transaction Counter | number of transactions in this block | 1-9 bytes |

| Transactions        | list of transactions                 | variable  |

Table 2.1: Bitcoin block structure

For PoW mining, we are only concerned with the 80-byte *block header* which is the input to the PoW algorithm. The data fields of a Bitcoin block header are shown in Table 2.2.

| Field               | Description                                     | Size     |

|---------------------|-------------------------------------------------|----------|

| Version             | number to track protocol updates                | 4 bytes  |

| Previous Block Hash | reference to previous block                     | 32 bytes |

| Merkle Root         | Merkle tree root for transactions in this block | 32 bytes |

| Timestamp           | approximate creation time of the block          | 4 bytes  |

| Difficulty Target   | encoded PoW target for this block               | 4 bytes  |

| Nonce               | a counter used for PoW                          | 4 bytes  |

Table 2.2: Bitcoin block header

The Bitcoin PoW algorithm, called SHA256D, is a double application of the standard SHA256 hash function, which takes the block header as input and outputs a 32-byte hash. Specifically, SHA256D is defined as:

SHA256D(x) = SHA256(SHA256(x))

If the resulting hash is numerically smaller, when interpreted as an unsigned integer, than a specific *target* value, then the block header input that produced the hash is considered a valid proof-of-work. The target is a 256-bit value that is derived from the 4-byte *difficulty target* that is contained within the block header. The difficulty target is encoded as a 24-bit significand and an 8-bit exponent, such that the actual target is calculated as:

significand

$$\times 256^{\text{exponent} - 3}$$

Miners are able to change a few fields of the block header as a source of variation in order to generate many different inputs to the PoW hash function. The miner is free to choose to include or not any transactions in the block and their ordering in the list, as long as all transactions are valid (i.e. correct accounting has been applied). This changes the *Merkle root* value in the block header, as it is a digest of all transactions in a block. The miner is also allowed to change the *timestamp* to a value that is greater than the median timestamp of the previous 11 blocks and less than the network adjusted time<sup>1</sup> plus 2 hours. Miners are also free to change the *nonce* field to any value of their choosing.

The Bitcoin mining algorithm is simply:

```

def mine_bitcoin(block_header):

while sha256d(block_header) >= target:

block_header.nonce += 1

return block_header

```

Once a miner finds a *wining* hash (meaning a hash that is smaller than the target), it broadcasts its version of the block to the rest of the network. If the network is satisfied that the rules for including transactions have been followed and the PoW is valid, then the winning miner will be credited with a freshly minted Bitcoin reward (6.25 Bitcoins as of 2020-2024) and the transaction fees for each transaction included in the block, and then that particular block is added to the blockchain. While it takes many trials for a miner to find a valid PoW, it only takes one hash for others to verify its validity.

The exact mechanism with which the winning miner is awarded Bitcoins is that, by protocol, every miner is allowed to set the first transaction in the block called the *coin-base transaction*, which is a transaction that mints new Bitcoins to a specified address. Typically the miner will set the receiving address for the coin-base transaction to an address they own.

The Bitcoin protocol adjusts the difficulty target every 2016 blocks in order to keep the expected *block interval* (i.e. the time between blocks being added to the chain), as close to 10 minutes as possible.

### 2.1.2 Pooled mining

Well-established blockchains are typically made up of thousands of individual miners. Thus, the likelihood of an individual miner winning a block is extremely low, which leads to a high variance in the frequency of their payouts. However, miners have regular operational

<sup>&</sup>lt;sup>1</sup>The network adjusted time is the median of the wall clock times returned by all other nodes that are connected to the miner.

costs, such as their electricity, maintenance, and labour costs. Therefore, it is common practice for smaller miners to pool their computational power and internally distribute their earnings according to the amount of computational power each miner brings to the pool. With their combined hash rate, the pool is more likely to find a valid PoW, which lowers the variance of payout frequency.

To prevent cheating by pool participants, called *workers*, the pool operator chooses which transactions are included in the block and, in particular, sets the coin-base transaction such that the payout is awarded to the pool itself, and not any of the workers. The pool provides a block header *template* to each individual worker connected to the pool, where the Merkle root is already set and the miners are only allowed to change the timestamp and nonce fields. To keep track of the amount of computational power each worker is contributing, the pool requires that the worker also reports any hashes that satisfy a much easier target (called the pool target) than the global target. This way, the pool is able to get frequent reports, called shares, which are essentially mini-PoWs that the pool can use to verify that the workers are working on the correct block header and to be able to estimate the hash rate contributed by each worker. Any hash that meets the global target will generate a payout to the pool itself, which is then distributed among the workers.

Pooled mining introduces the risk that the pool operator refuses to pay out. In such cases the individual miner can only cut their losses and switch to a different pool.

## 2.1.3 Evolution of mining hardware

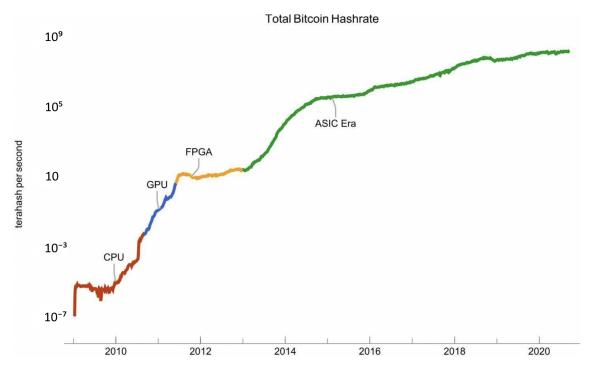

Initially, on blockchains such as Bitcoin, miners were able to use commodity hardware such as CPUs and GPUs to perform proof-of-work. As cryptocurrency mining became more financially lucrative, miners sought to gain efficiency advantages over their competitors by utilizing specialized hardware. In [3] a timeline following the evolution of Bitcoin hardware was summarised, with CPUs dominating the network until late 2010, after which GPUs and FPGAs took over and then finally ASICs started dominating the network from 2013.

In Figure 2.1 we plot the historical Bitcoin network hashrate, marking the different mining hardware  $eras^2$ . The increase in total network hash rate is driven by a combination of

<sup>&</sup>lt;sup>2</sup>data from https://www.blockchain.com/charts/hash-rate, eras from [3]

more miners coming onto the network (due to Bitcoin's price increasing) and technological advancements in mining hardware.

Figure 2.1: Bitcoin network hashrate

Typically for the SHA256D PoW algorithm, CPUs, GPUs, FPGAs, and ASICs are able to achieve on the order of tens to hundreds of mega-hashes per second, hundreds of megahashes to giga-hashes per second, giga-hashes to tens of giga-hashes per second, and terahashes per second respectively.

## 2.1.4 ASIC-resistance

Due to ASICs having a high barrier to entry for the average consumer and the at-home miner, it is feared by the crypto-community, as surveyed in [28], that cryptocurrency mining will become increasingly centralized among large ASIC farms and ASIC manufacturers. Therefore, many cryptocurrencies (e.g. Ethereum [8] and RavenCoin [11]) decided to introduce forms of ASIC-resistance into their PoW algorithms. We consider three main classes of ASIC-resistant algorithms; multi-hash, memory-hard, and algorithmic.

#### 2.1.4.1 Multi-hash

One example of a multi-hash PoW algorithm is X11 [10], which chains together eleven hash functions in order; Blake, BMW, Grøstl, JH, Keccak, Skien, Luffa, Cubehash, Shavite, Simd and Echo. A descendant of X11 is X16R [7] which uses up to sixteen different hash functions (all SHA3 Round 2 candidates plus whirlpool and SHA512). However, while X11 uses a fixed chain of hash functions, the sequence of hash functions is randomised for every new block in X16R. Additionally, the same hash function can appear more than once in the chain of sixteen, or not at all.

In [9], the author aimed to assess the ASIC-resistance of multi-hash proof-of-work algorithms. Three types of multi-hash PoW algorithms were identified: fixed sequence hash chains (e.g. X11), hash chains with a variable sequence per block (e.g. X16R), and hash chains with a variable sequence per nonce.

The author then detailed three hardware platforms which were used for their experiments, an Intel i7-8700K CPU, an NVIDIA GeForce GTX 1080 Ti GPU and a Xilinx Zynq UltraScale+ ZU9EG FPGA. The FPGA platform was used to stand-in for ASICs, as they are commonly used to prototype ASICs and have implementation characteristics that allow prediction of ASIC performance. Due to the usage of an FPGA instead of an ASIC and the difference in price of the three hardware platforms, the author measured performance relative to a SHA256D baseline implementation for each of the three setups. The author proposed a metric called the ASIC-disadvantage metric, which is the ratio of the relative performance loss when going from SHA256D to a multi-hash chain algorithm when implemented using an FPGA compared to the loss in performance when implemented on other platforms. In order to demonstrate ASIC-resistance, a tested algorithm must have an ASIC-disadvantage of greater than one, and ideally significantly greater than one.

In the experiment, the author implemented the following algorithms on an FPGA:

- a fixed hash chain sequence using a fixed pipeline,

- a hash chain sequence that varies per block, using a crossbar that connects the hash cores, and

- a hash chain sequence that varies per nonce, using a crossbar that connects the hash cores.

It was shown that both the fixed chain algorithm and a version of the hash chain sequence that varies per block, but where no two hash functions were reused, were not able to achieve an ASIC-disadvantage of 1.0. However the version of variable sequence hash chain per block, where hash functions could be reused, achieved an ASIC-disadvantage of 1.33 relative to GPUs. In the case of variable sequence hash chain per nonce, the experiment showed a significant performance loss for GPUs due to control flow divergence and was therefore not able to achieve an ASIC-disadvantage of 1.0.

In the article, the author describes implementing the variable sequence hash chain algorithm (with 15 hash functions) using a 16x16 crossbar to connect the hash cores. This introduced a small overhead in resource usage, while offering low latency and high bandwidth. However, if we design an algorithm that uses hundreds of different hash functions, the resource overhead used up by a crossbar grows at an  $O(n^2)$  rate, where n is the number of hash functions. This overhead quickly becomes unsustainable. In such a situation an ASIC must instead use a more scalable network topology, such as a ring, and thus sacrifice latency and bandwidth. For CPUs and GPUs, increasing the number of hash function should only increase the program size and have an insignificant effect on performance.

ASIC mining hardware has been available for fixed-chain multi-hash algorithms since 2016. As of writing, the highest performing X11 miner is the Bitmain Antminer  $D7^3$ , which achieves a hash rate of 1.157 TH/s.

A miner which was advertised as the OW1 ASIC<sup>4</sup>, was released in late 2019, which marketed an X16R hash rate of 182 MH/s, while consuming 1400 watts. It is speculated by the community that these OW1 ASICs have an FPGA-like, reconfigurable architecture.

#### 2.1.4.2 Memory-hard

Memory-hard PoW algorithms are intentionally designed to require a large memory capacity or to be bottlenecked by memory bandwidth, and usually a combination of both. The rationale for this is that fast on-chip memory is typically SRAM-based, which is low in capacity, therefore if the algorithm requires access to a dataset (typically sized at sev-

<sup>&</sup>lt;sup>3</sup>Bitmain Antminer D7:

https://shop.bitmain.com/product/detail?pid=00020210721103817933De3r7nxP06AD

<sup>&</sup>lt;sup>4</sup>OW1 ASIC:

https://en.cryptonomist.ch/2019/09/17/mining-ravencoin-hashrate/

eral gigabytes) that is much larger than the amount of SRAM that can fit onto an ASIC, an external memory is needed. However, external memory bandwidth is limited by the number of I/O pins on the chip. The I/O limitation was thought to level the playing field between ASICs and off-the-shelf hardware such as CPUs, GPUs, and FPGAs, as it was thought that it would be impractical to build an ASIC with an order of magnitude more I/O pins than is already generally available.

Examples of memory-hard PoW algorithms include, Ethash [8], Equihash [5], and CuckooCycle [32]. Ethash is currently the second most popular PoW algorithm, behind Bitcoin's SHA256D. A detailed description of Ethash can be found in Appendix A.1.

GPUs are most commonly used for mining memory-hard PoW. However, recently both FPGA and ASIC miners for Ethash became available. Commercial implementations of Ethash using the Xilinx Virtex Ultrascale+ HBM series of FPGAs<sup>5</sup> are able to outperform GPUs<sup>6</sup> in efficiency by 1.8x. The Jingle Mining Jasminer X4<sup>7</sup> is an ASIC composed of two silicon dies, a logic die and a DRAM die, which are vertically stacked. The device is able to achieve 1TB/s memory bandwidth while consuming very little energy, and outperforms FPGA implementations by 3.1x in efficiency.

#### 2.1.4.3 Algorithmic

Algorithmic PoW algorithms work by generating a new instruction-based random program for each block interval. The randomly generated programs are typically designed to stress as many components of a standard x86 CPU as possible. Branch instructions are also used so that a branch predictor is required to achieve good performance. This type of PoW is CPU-biased and can not be efficiently mined by GPUs, FPGAs or ASICs.

The only example of an algorithmic PoW that is used in practice is RandomX [30], which is the PoW for the Monero cryptocurrency. A detailed description of RandomX can be found in Appendix A.2.

$<sup>^5 \</sup>rm Xilinx$  Varium C1100 card (with 460GB/s of memory bandwidth) achieves  ${\sim}73\rm MH/s$  in Ethash while using  ${\sim}81\rm W.$

https://github.com/todxx/teamredminer

$<sup>^6\</sup>mathrm{NVIDIA}$  RTX 3070 (with 448 GB/s of memory bandwidth) achieves  ${\sim}60\mathrm{MH/s}$  in Ethash while using  ${\sim}120\mathrm{W}.$

https://www.nicehash.com/profitability-calculator/nvidia-rtx-3070

$<sup>^{7}</sup>$ Jasminer X4 achieves ~64MH/s while using ~23W.

https://www.jinglemining.com/pages/about-jasminer-x4

## 2.2 FPGA runtime reconfiguration

Modern FPGAs can be dynamically reconfigured at runtime without needing to be powercycled. Most basic resources in the FPGA fabric can be selectively and partially reconfigured without disrupting the ongoing operation of the surrounding logic. FPGA configuration data are called bitstreams, whereas configuration data that configures only a portion of the FPGA are called partial bitstreams. In this section, we will examine the FPGA architectures from Xilinx and Intel in regards to their runtime reconfiguration capabilities, and outline some previous work in the area of runtime reconfiguration.

### 2.2.1 FPGA hardware

#### 2.2.1.1 Xilinx Virtex Ultrascale+

The Xilinx Virtex Ultrascale+ family of FPGAs is manufactured on TSMC's 16nm technology node and has been available since 2016. These devices are constructed from one to four silicon dies called super logic regions (SLRs). The SLRs are stacked on top of a single passive silicon substrate and are electrically connected to each other using through-silicon vias (TSVs) and wires in the silicon substrate. The High-Bandwidth Memory (HBM) variant of these devices also contains up to two DRAM dies, which are co-packaged in the same manner alongside the SLRs. The amount of routing between SLRs is limited, so care must be taken when partitioning large designs across SLRs. The maximum number of LUTs contained within a Virtex Ultrascale+ SLR is ~440K.

These FPGAs can be reconfigured at runtime by writing a partial bitstream to the *Internal Configuration Access Port* (ICAP). The time taken to reconfigure a module is equal to the time it takes to load the partial bitstream. For Virtex Ultrascale+, the ICAP has a maximum clock frequency of 200MHz and is 32-bits wide, giving a throughput of 800MB/s, meaning that a 20MB partial bitstream, which is large enough to configure an entire SLR, can be loaded in 25ms. Each SLR has a separate ICAP, one of which is designated the master ICAP. The master ICAP can be used to reconfigure any SLR at a reduced clock frequency of 125MHz (500MB/s). However, each ICAP can configure its local SLR at the maximum clock frequency of 200MHz [38] and in parallel.

Chips from this family such as the VU9P, VU13P, and the HBM-enabled VU33P, VU35P,

and U55N are all popular in the cryptocurrency mining community. There have been several mining targeted boards utilizing these chips, including the SQRL FK33<sup>8</sup>, SQRL JC-series, Bittware CVP-13<sup>9</sup>, derivatives of the Xilinx VCU1525<sup>10</sup>, and most recently the Xilinx Varium C1100 blockchain accelerator card<sup>11</sup>.

## 2.2.1.2 Intel Stratix 10

Intel's Stratix 10 family of FPGAs is manufactured on the Intel 14nm node and consists of a single monolithic logic die, where the FPGA fabric resides, and several smaller surrounding dies which can be memory, transceivers, or ASICs. The separate dies are connected using a packaging technology called Embedded Multi-Die Interconnect Bridge (EMIB).

The FPGA fabrics of these devices consists of an array of identical logical sectors [18], such that any module that fits completely within a sector can be relocated to any other sector without the need for recompilation. This feature can be used to implement designs that utilize course-grained module relocation. The FPGA fabric architecture is very suitable for deeply pipelined designs due to the *hyper-flex* architecture, which adds millions of pipeline registers within the switch fabric itself, allowing the designer to be more liberal with pipeline register usage.

There is one dedicated *secure device manager* (SDM), which handles loading partial bitstreams. However, the maximum clock frequency for the 32-bit configuration bus is 125MHz. The relatively slow configuration speed (especially if we consider parallel ICAP usage) coupled with the fact that the maximum bitstream size for Stratix 10 is similar to that of Virtex Ultrascale+, means that reconfiguration of Stratix 10 devices is much slower than for Virtex Ultrascale+ devices.

Compared to Xilinx FPGAs, there are not many Intel FPGAs that are currently being used for mining.

$<sup>^8</sup> Squirrels Research Labs LLC is defunct as of 2021, their product page is no longer on the web. <math display="inline">^9 \rm https://www.bittware.com/cvp-13/$

<sup>&</sup>lt;sup>10</sup>Such as the SQRL BCU1525, the Osprey Mining ECU200, and the TUL BTU9P.

https://shop.fpga.guide/products/btu9p-by-tul?variant=14315446861936

<sup>&</sup>lt;sup>11</sup>https://www.xilinx.com/products/accelerators/varium/c1100.html

## 2.3 Related Work

We do not know of any other academic work that has been done regarding the application of FPGA runtime reconfiguration to proof-of-work algorithms. However, there has been much previous work in the field of FPGA runtime reconfiguration.

## 2.3.1 Applications of runtime reconfiguration

With current FPGA hardware, it takes a significant amount of time, depending upon its size, to reconfigure a module — typically on the order of several milliseconds. Therefore there is a significant overhead involved when applying runtime reconfiguration. Still, there are many applications that greatly benefit from runtime reconfiguration, as discussed in the literature.

One common use case for runtime reconfiguration is for image or video processing pipelines, where large amounts of data are streamed through multiple filter stages. In real-time camera applications, where perhaps image quality changes throughout the day, different filters may be needed. A static design, with all the potential filters already baked in, consumes more power and requires a larger FPGA, when compared to a runtime reconfigurable approach, where only the filters that are needed are configured on the FPGA. In [4] the authors implemented two video processing filters on a Virtex-4 FPGA and showed an FPGA resource saving of almost 50 percent.

In [24] the authors demonstrated a time-shared computer vision pipeline, where multiple different processing pipelines can be time-multiplexed to serve different users. Their processing pipeline consists of several identically-sized reconfigurable partitions that are connected to a crossbar interconnect. Each reconfigurable partition can implement several reconfigurable processing modules, such as edge detection, colour-based object tracking, and template tracking. Up to two 1080p video frames are processed at a time, which are streamed from one reconfigurable module to another. Once the two frames have finished processing, the reconfigurable modules are replaced by modules that are needed for a different pipeline. They showed that their time-multiplexed approach is capable of processing a 1080p video through three different pipelines at 30Hz, when implemented on a Xilinx ZC706 board, with a Zynq FPGA. In [21] the authors presented a scalable H.264/AVC de-blocking filter that uses runtime reconfiguration to adapt to changes in the video resolution or frame-rate. They did this to improve throughput and save power by selecting the most performant processing implementation for each situation.

Another common application for runtime reconfiguration is software-defined radio (SDR), which is able to operate across multiple radio standards. Traditional custom ASICs with fixed function processing units are not flexible enough to implement SDR. However, purely software-based solutions have high latency and therefore can not be used for some applications. In [26], the authors present an *end-to-end multi-standard OFDM transceiver architecture*, that uses FPGA runtime reconfiguration to support rapid switching between three different standards: IEEE 802.11, IEEE 802.16, and IEEE 802.22. To avoid link disruption, the incoming data is buffered in memory during reconfiguration.

In [25], a high performance DES encryption implementation is presented that takes advantage of FPGA runtime reconfiguration by specialising the encryption circuit on a keyby-key basis. For symmetric key encryption, typically the encryption key, is the same for the entire connected session. By substituting the key into the circuit as a constant, the circuit can be greatly simplified. The author presents a tool *JBits*, which is capable of creating and modifying bitstreams with LUT contents that are specialized to a certain key. By this method, they observed better performance than a DES ASIC.

## 2.3.2 Runtime reconfiguration methodology

In [22], the authors describe three styles of layout for reconfigurable modules; island-style, slot style and grid style. In an island style layout, the FPGA is divided into islands that are capable of containing any reconfigurable module. However this method leads to under-utilization of resources as islands must be sized according to the largest module. In a slot-style layout, the FPGA is divided along one dimension (e.g. horizontally) into smaller slots where reconfigurable modules are allowed to take up multiple slots. The grid layout is similar to the slot layout with the difference being that the FPGA is divided in two dimensions creating a grid of reconfigurable regions.

In [2], the authors present a tool for module relocation, that is the ability to move a pre-implemented module from one location on the FPGA fabric to another. This can be

done without pre-defining the layout of boundaries for each reconfigurable partition as in [22]. This allows for denser packing of reconfigurable modules and thus better utilisation of FPGA resources.

# Chapter 3

# **Design** exploration

# 3.1 X16R algorithm

The X16R algorithm is a PoW algorithm that was primarily used by the cryptocurrency RavenCoin [11], which had an average block interval of one minute. The algorithm was used from January 2018 to May 2020, after which RavenCoin switched to a memory-hard PoW called KawPow [19], due to the threat of ASIC and FPGA miners outcompeting GPU miners [6].

### 3.1.1 Definition

The X16R algorithm is a hash algorithm, consisting of the chained application of these sixteen hash functions: (0) Blake, (1) BMW, (2) Groestl, (3) JH, (4) Keccak, (5) Skein, (6) Luffa, (7) Cubehash, (8) Shavite, (9) Simd, (A) Echo, (B) Hamsi, (C) Fugue, (D) Shabal, (E) Whirlpool, and (F) SHA512. With the exception of Whirlpool [31] and SHA512 [29], each hash function was submitted to the NIST SHA3 competition and passed to at least round 2 [33]. Each hash function is assigned a hexadecimal identifier (0x0 - 0xF). The order in which the hash functions are applied is determined by the last sixteen nibbles of the hash of the previous block header. For example, if the previous block was:

####

Then reading the right-most sixteen hexadecimal digits of the hash from left to right, we find the hash chain ordering:

```

which translates to:

```

```

Shabal -> Echo -> Keccak -> Luffa -> ... -> Simd -> Blake

```

The X16R hash function is described by the following pseudo-code:

```

hash_functions = [

blake, bmw, groestl, jh, keccak, skein, luffa, cubehash,

shavite, simd, echo, hamsi, fugue, shabal, whirlpool, sha512

]

def x16r(header):

order = get_last_16_nibbles(header.prev_hash)

midstate = header

for i in order:

midstate = hash_functions[i](midstate)

return midstate

```

Note that the input into the first hash function is the 80-byte block header, which is the typical header size for many blockchains. However, as all hash functions in X16R produce a 64-byte digest, all subsequent function applications take a 64-byte input.

#### 3.1.2 Properties

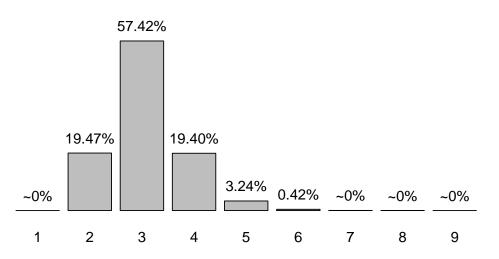

As the ordering of the hash functions is determined by the hash of the previous block header, we can assume the that ordering is effectively uniformly random. We note that there is the possibility of a hash function occurring more than once in the chain, we call these occurrences *repetitions*.

The probability of there being no repetitions in an X16R chain is the number of chains where each hash function is unique, i.e. 16!, divided by the total possible number of chain permutations i.e.  $16^{16}$ :

$$\frac{16!}{16^{16}} \approx 1.134 \times 10^{-6}$$

We can see that the case with no repetitions is extremely unlikely, around one in a million. This presents a challenge for hardware implementation, as a design with only one hash core per function will almost always be bottlenecked when that core is needed more than once to complete processing the X16R chain.

Figure 3.1 shows the probability of an X16R chain having a function that occurs N times, and all other functions occurring at most N times.

Figure 3.1: Probability of X16R chain having a function that occurs N times, and all other functions occurring at most N times

In the following sections, we will consider three different types of FPGA-based architectures for implementing the X16R algorithm.

## 3.2 Static design

First we consider the naive approach of a static design, in which sixteen different hash cores are instantiated on a single FPGA and are connected to each other through an infabric network. A suitable means of transferring the output of one core to the input of the next is therefore sought. As each hash core is fully unrolled, they can produce one result for every clock cycle. Therefore, the communication between each subsequent core in the chain is a continuous stream. One might initially consider a crossbar switch, which allows non-blocking communication between any pair of cores. However, a crossbar has a wiring complexity of  $O(n^2)$  and requires 578 connections for a 17x17 bidirectional crossbar (17x17 because there are 16 hash functions and 1 input/output port). If we assume that each connection is 512-bits wide (a requirement for fully unrolled hash cores), we would require 295,936 wires, which is a significant demand on an FPGA's routing resources. Moreover, most of the switches and wires are not utilized during the processing of any particular instance of X16R. However, the network complexity is not the main concern when implementing a static design. In Figure 3.1, we see that most of the time, there are repetitions in the chain. One can calculate that, on average, a static design with only one core per hash function is bottle-necked at 34.4% of its peak throughput. This is because only a few cores are highly utilized (due to being needed multiple times in the chain), while most other cores are under-utilized (waiting for data or not needed). Another challenge is the amount of FPGA resources required to implement the fully static design. It is possible to fit rolled-up versions of each hash core in a modern FPGA. We see in [9] an implementation of X15R (X16R without Whirlpool) using a crossbar switch on a Xilinx ZU9EG device, however the performance is poor, achieving only 2MH/s. In order to achieve higher performance we need to unroll the hash cores. However, an X16R design consisting of sixteen fully unrolled hash cores will require an extremely large FPGA.

If we take the resource utilization numbers from our own hash core library, described in Section 4, we require a device with over 2.3M 6-input LUTs (not accounting for the crossbar) in order to accommodate one instance of each function. By comparison, the largest Xilinx Ultrascale+ device that is obtainable by miners, the VU13P, has 1.7M LUTs. An even larger device, the VU19P with 4M LUTs, is sold by Xilinx, however, they are likely to be too few in number and too expensive to be financially viable for miners. In order to meet the area requirements for a fully static design, one may attempt to team multiple FPGAs and spread the hash cores across them. However, it is difficult to extend the crossbar off-chip due to the lack of wires (parallel approach) or lack of ser-des bandwidth (serial approach).

## 3.3 Dynamic full chain